- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360999 > ISP1761ET (NXP SEMICONDUCTORS) Hi-Speed Universal Serial Bus On-The-Go controller PDF資料下載

參數(shù)資料

| 型號(hào): | ISP1761ET |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | Hi-Speed Universal Serial Bus On-The-Go controller |

| 中文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PBGA128 |

| 封裝: | 9 X 9 MM, 0.80 MM HEIGHT, PLASTIC, MO-195, SOT857-1, TFBGA-128 |

| 文件頁數(shù): | 105/158頁 |

| 文件大小: | 724K |

| 代理商: | ISP1761ET |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁當(dāng)前第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁

9397 750 13258

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 01 — 12 January 2005

105 of 158

Philips Semiconductors

ISP1761

Hi-Speed USB OTG controller

[1]

First NAK: The first NAK on an IN or OUT token after a previous ACK response.

10.4.4

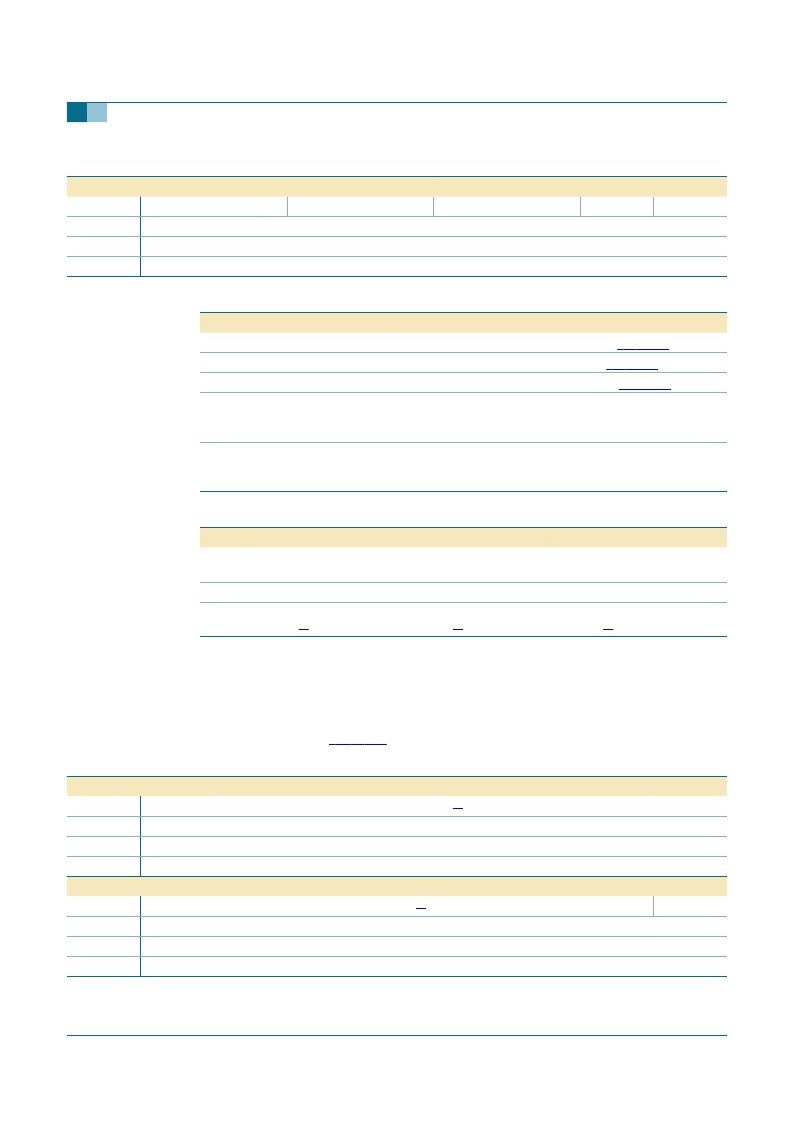

Debug register (R/W: 0212h)

This register can be accessed using address 0212h in 16-bit bus access mode or using

the upper-two bytes of the Interrupt Configuration register in 32-bit bus access mode. For

the bit allocation, see

Table 101

.

[1]

The reserved bits should always be written with the reset value.

Table 98:

Bit

Symbol

Reset

Bus reset

Access

Interrupt Configuration register: bit allocation

7

6

CDBGMOD[1:0]

1

1

1

1

R/W

R/W

5

4

3

2

1

0

DDBGMODIN[1:0]

1

1

R/W

DDBGMODOUT[1:0]

1

1

R/W

INTLVL

0

unchanged

R/W

INTPOL

0

unchanged

R/W

1

1

1

1

R/W

R/W

Table 99:

Bit

7 to 6

5 to 4

3 to 2

1

Interrupt Configuration register: bit description

Symbol

Description

CDBGMOD[1:0]

Control 0 Debug Mode:

For values, see

Table 100

DDBGMODIN[1:0]

Data Debug Mode IN:

For values, see

Table 100

DDBGMODOUT[1:0]

Data Debug Mode OUT:

For values, see

Table 100

INTLVL

Interrupt Level

: Selects the signaling mode on output INT

(0 = level; 1 = pulsed). In the pulsed mode, an interrupt

produces a 60 ns pulse. Bus reset value: unchanged.

INTPOL

Interrupt Polarity:

Selects signal polarity on output INT

(0 = active LOW; 1 = active HIGH). Bus reset

value: unchanged.

0

Table 100: Debug mode settings

Value

CDBGMOD

00h

interrupt on all ACK and

NAK

01h

interrupt on all ACK

1Xh

interrupt on all ACK and

first NAK

[1]

DDBGMODIN

interrupt on all ACK and

NAK

interrupt on ACK

interrupt on all ACK and

first NAK

[1]

DDBGMODOUT

interrupt on all ACK, NYET and

NAK

interrupt on ACK and NYET

interrupt on all ACK, NYET and

first NAK

[1]

Table 101: Debug register: bit allocation

Bit

15

Symbol

Reset

0

Bus reset

0

Access

R/W

Bit

7

Symbol

Reset

0

Bus reset

0

Access

R/W

14

13

12

11

10

9

8

reserved

[1]

0

0

0

0

0

0

0

0

0

0

0

0

0

0

R/W

6

R/W

5

R/W

4

R/W

3

R/W

2

R/W

1

R/W

0

DEBUG

0

0

R/W

reserved

[1]

0

0

R/W

0

0

0

0

0

0

0

0

0

0

R/W

R/W

R/W

R/W

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP2100A | Telecommunication IC |

| ISP2100BN4 | Microprocessor |

| ISP2300 | Controller Miscellaneous - Datasheet Reference |

| ISP2310 | Controller Miscellaneous - Datasheet Reference |

| ISP2312 | Controller Miscellaneous - Datasheet Reference |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1761ET,518 | 功能描述:USB 接口集成電路 USB 2.0 HS OTG HOST RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ET,551 | 功能描述:USB 接口集成電路 DO NOT USE ORDER -T OR NO "-" RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ET,557 | 功能描述:USB 接口集成電路 USB 2.0 HS OTG HOST RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1761ETGE | 功能描述:IC USB CTRL HI-SPEED 128TFBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| ISP1761ET-S | 功能描述:IC USB OTG CONTROLLER 128TFBGA RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。