- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄377496 > Intel387 sx (Intel Corp.) SX Math Coprocessor(32位數(shù)學協(xié)處理器) PDF資料下載

參數(shù)資料

| 型號: | Intel387 sx |

| 廠商: | Intel Corp. |

| 英文描述: | SX Math Coprocessor(32位數(shù)學協(xié)處理器) |

| 中文描述: | 山西數(shù)學協(xié)處理器(32位數(shù)學協(xié)處理器) |

| 文件頁數(shù): | 15/47頁 |

| 文件大?。?/td> | 443K |

| 代理商: | INTEL387 SX |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁

Intel387

TM

SX MATH COPROCESSOR

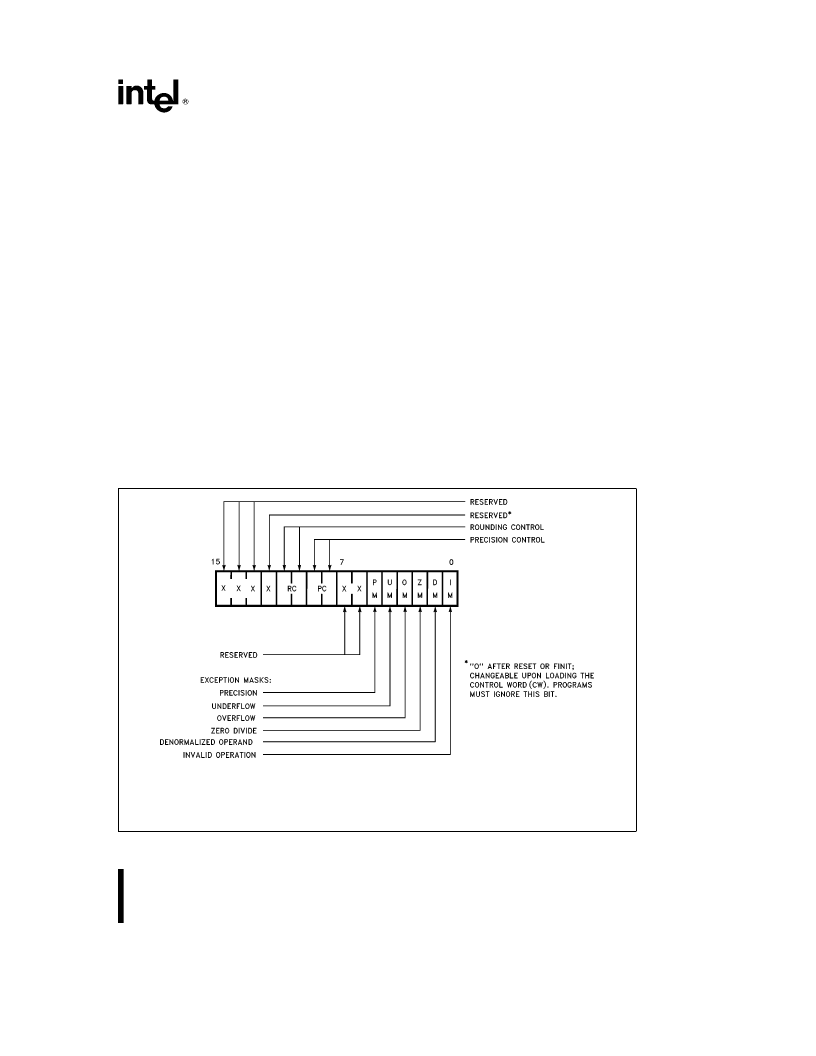

3.2.2 CONTROL WORD (CW) REGISTER

The Math CoProcessor provides the programmer

with several processing options that are selected by

loading a control word from memory into the control

register. Figure 3-3 show the format and encoding of

fields in the control word.

The low-order byte of the control word register is

used to configure the exception masking. Bits 5–0

of the control word contain individual masks for each

of the six exceptions that the Math CoProcessor rec-

ognizes. See Section 3.5, Exception Handling, for

further explanation on the exception control and def-

inition.

The high-order byte of the control word is used to

configure the Math CoProcessor operating mode, in-

cluding precision, rounding and infinity control.

#

The rounding control (RC) field (bits 11–10) pro-

vide for directed rounding and true chop, as well

as the unbiased round to nearest even mode

specified in the IEEE standard. Rounding control

affects only those instructions that perform

rounding at the end of the operation (and thus

can generate a precision exception); namely,

FST, FSTP, FIST, all arithmetic instructions (ex-

cept FPREM, FPREM1, FXTRACT, FABS, and

FCHS) and all transcendental instructions.

#

The precision control (PC) field (bits 9–8) can be

used to set the Math CoProcessor internal oper-

ating precision of the significand at less than the

default of 64 bits (extended precision). This can

be useful in providing compatibility with early gen-

eration arithmetic processors of smaller preci-

sion. PC affects only the instructions FADD,

FSUB(R), FMUL, FDIV(R), and FSQRT. For all

other instructions, either the precision is deter-

mined by the opcode or extended precision is

used.

#

The ‘‘infinity control bit’’ (bit 12) is not meaningful

to the Intel387 SX Math CoProcessor and pro-

grams must ignore its value. To maintain compat-

ibility with the 8087 and 80287 (non-387 core),

this bit can be programmed, however, regardless

of its value the Intel387 SX Math CoProcessor

always treats infinity in the affine sense (

b

%

k

a

%

). This bit is initialized to zero both after a

hardware reset and after FINIT instruction.

All other bits are reserved and should not be pro-

grammed, to assure compatibility with future proces-

sors.

240225–5

Precision Control

00D24 bits (single precision)

01D(reserved)

10D53 bits (double precision)

11D64 bits (extended precision)

Rounding Control

00DRound to nearest or even

01DRound down (toward

b

%

)

10DRound up (toward

a

%

)

11DChop (truncate toward zero)

Figure 3-3. Control Word

15

15

相關PDF資料 |

PDF描述 |

|---|---|

| INTEL486 GX | Emedded Ultra-Low Power INTEL486 GX Processor(嵌入式超低能量處理器) |

| INTEL486 SX | Emedded Ultra-Low Power INTEL486 SX Processor(嵌入式超低能量處理器) |

| INTEL82801 | 82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | Firmware Hub (FWH) |

| INTELDX2 | High-Performance 32-Bit Embedded Processor(高性能32位嵌入式處理器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| INTEL387TMDX | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Intel387TM DX MATH COPROCESSOR |

| INTEL740 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:64-Bit Graphics (GUI) Accelerator |

| INTEL82801 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:82801AB (ICH0) I/O Controller Hub |

| INTEL82802AB | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:Firmware Hub (FWH) |

| INTELLIGENT CHARGER + 4AA | 制造商:Energizer 功能描述:Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。