- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67684 > IBM25PPC970FX6UB267ET 64-BIT, 1800 MHz, RISC PROCESSOR, CBGA576 PDF資料下載

參數(shù)資料

| 型號: | IBM25PPC970FX6UB267ET |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 64-BIT, 1800 MHz, RISC PROCESSOR, CBGA576 |

| 封裝: | 25 X 25 MM, 1 MM PITCH, CERAMIC, BGA-576 |

| 文件頁數(shù): | 61/78頁 |

| 文件大小: | 3524K |

| 代理商: | IBM25PPC970FX6UB267ET |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁

Datasheet

PowerPC 970FX RISC Microprocessor

System Design Information

Page 64 of 78

Version 2.5

March 26, 2007

The bus frequency multiplier ratio typically indicates the required PLL multiplier setting. Ratios based on

multiples of 3 (3:1, 6:1, 12:1) should always use PLLMULT = ‘0’ (low) for a PLL multiplier of 12. The required

core frequency should be divided by 12 to determine the required input SYSCLK frequency. Ratios based on

multiples of 2 (2:1, 4:1, 8:1, 16:1) should always use PLLMULT = ‘1’ (high) to multiply SYSCLK by 8.

Note: Using bus frequency ratios of 3:1, 6:1 or 12:1 with PLLMULT = 1 or ratios of 8:1 or 16:1 with

PLLMULT = 0 is not recommended. Internal clock synchronization delays might reduce performance.

After the correct BUS_CFG(0:2) and PLLMULT pin settings are determined, the required SYSCLK input

frequency can be determined. The selected SYSCLK input frequency should be within the minimum and

maximum frequencies specified in Table 3-8 Clock ac Timing Specifications on page 26.

5.2.2 PLL_RANGE Configuration

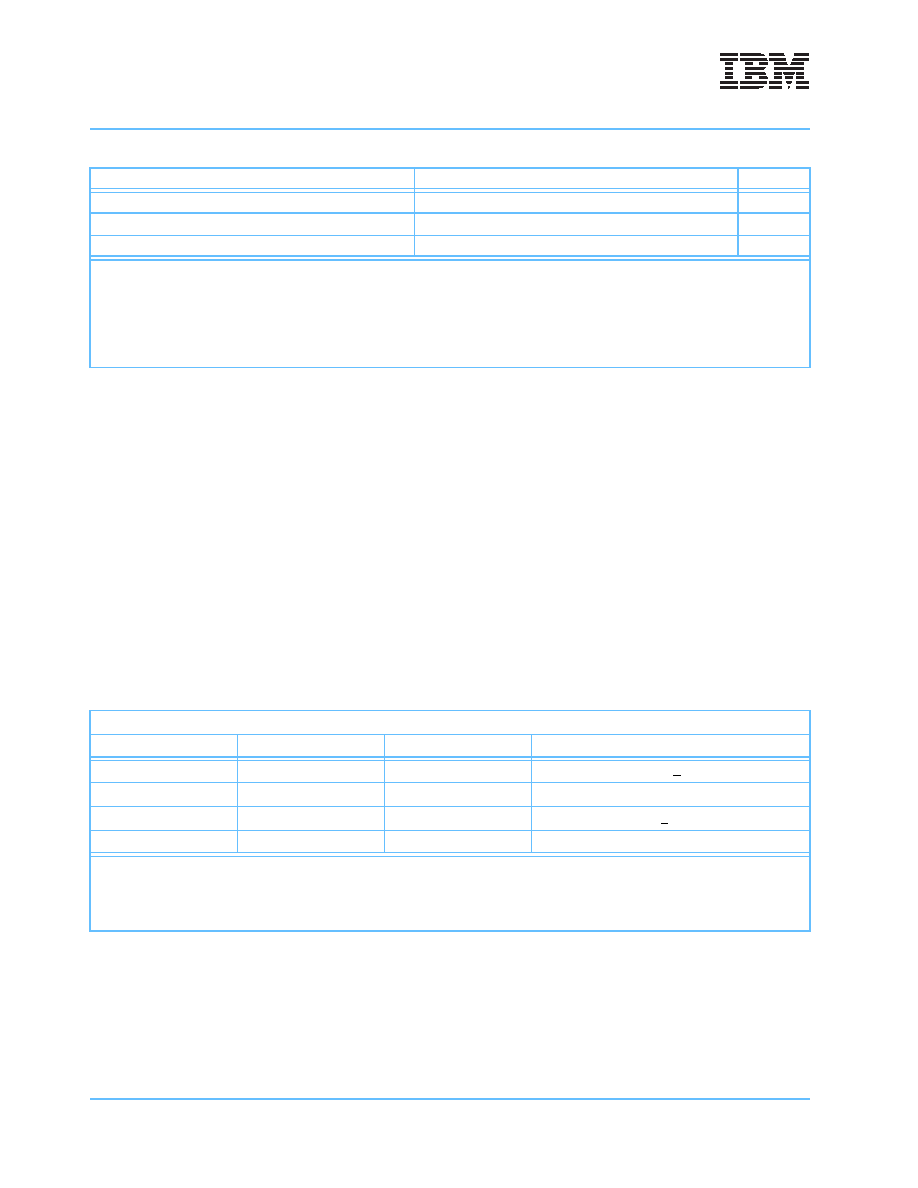

Table 5-2 shows the PLL voltage controlled oscillator (VCO) configuration for the PowerPC 970FX, using the

pins PLL_RANGE1 and PLL_RANGE0.

5.2.3 Typical PLL and SYSCLK Configurations

Table 5-3 provides a few examples of typical system configurations.

101

12:1

3

110

16:1

1

111

Not valid

Table 5-2. PowerPC 970FX RISC Microprocessor PLL Configuration

PLL_RANGE(1:0) Settings

Range Name

PLL_RANGE1

PLL_RANGE0

Frequency Range

Low

0

Frequency < 1.2 GHz

Medium

0

1

1.2 GHz < Frequency < 1.8 GHz

High

1

0

1.8 GHz < Frequency

Reserved

1

Reserved

Notes:

1. The PLL_MULT and PLL_RANGE(1:0) bits can be overwritten by JTAG commands, and the BUS_CFG bits can be changed by

SCOM commands, during the POR sequence. See the 970FX PowerPC 970FX Power On Reset Application Note for more details.

2. PLL frequency range settings are not an indicator of available PowerPC 970FX processor speeds.

Table 5-1. PowerPC 970FX RISC Microprocessor Bus Configuration (Page 2 of 2)

BUS_CFG(0:2)

Ratio

Notes

Note: BUS_CFG bits can be changed by SCOM commands during the POR sequence. See the PowerPC 970FX Power On Reset

Application Note.

Notes:

1. Bus ratios of 8:1 and 16:1 are not supported for processor interface (PI) input functionality or for power tuning.

2. Limited power-tuning frequency scaling.

3. No power-tuning frequency scaling.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| IBM25PPC970MP7TR21AFT | 64-BIT, 1600 MHz, RISC PROCESSOR, CBGA575 |

| IBM26BL486DX2-V66QP | 32-BIT, 66 MHz, MICROPROCESSOR, PQFP208 |

| IBM26BL486DX2-V80QP | 32-BIT, 80 MHz, MICROPROCESSOR, PQFP208 |

| IBM26BL486DX2-V50GP | 32-BIT, 50 MHz, MICROPROCESSOR, CPGA168 |

| IBM26BL486DX2-V50QP | 32-BIT, 50 MHz, MICROPROCESSOR, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IBM25PPC970FX6UB429RT | 制造商:IBM Microelectronics 功能描述:MPU 970FX RISC 64BIT 90NM 1.5V 576CBGA - Trays 制造商:IBM 功能描述:IBM IBM25PPC970FX6UB429RT Co-Processors |

| IBM25PPC970GX7TR01-ET | 制造商:IBM 功能描述:ANTARES GX DD1.0X 1.2GHZ POWER OPTIMIZED - Trays |

| IBM25PPC970GX7TR05-ET | 制造商:IBM 功能描述:ANTARES GX DD1.0X 1.4GHZ POWER OPTIMIZED - Trays |

| IBM25PPC970GX7TR20-ET | 制造商:IBM Microelectronics 功能描述:ANTARES GX DD1.0X 1.6GHZ POWER OPTIMIZED - Trays |

| IBM25PPC970GX7TR23-ET | 制造商:IBM 功能描述:ANTARES GX DD1.0X 1.6GHZ PERFORMANCE OPTIMIZED - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。