- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GCIXP1250-200 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | GCIXP1250-200 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 72/148頁(yè) |

| 文件大小: | 1601K |

| 代理商: | GCIXP1250-200 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)當(dāng)前第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)

Intel

IXP1250 Network Processor

72

Datasheet

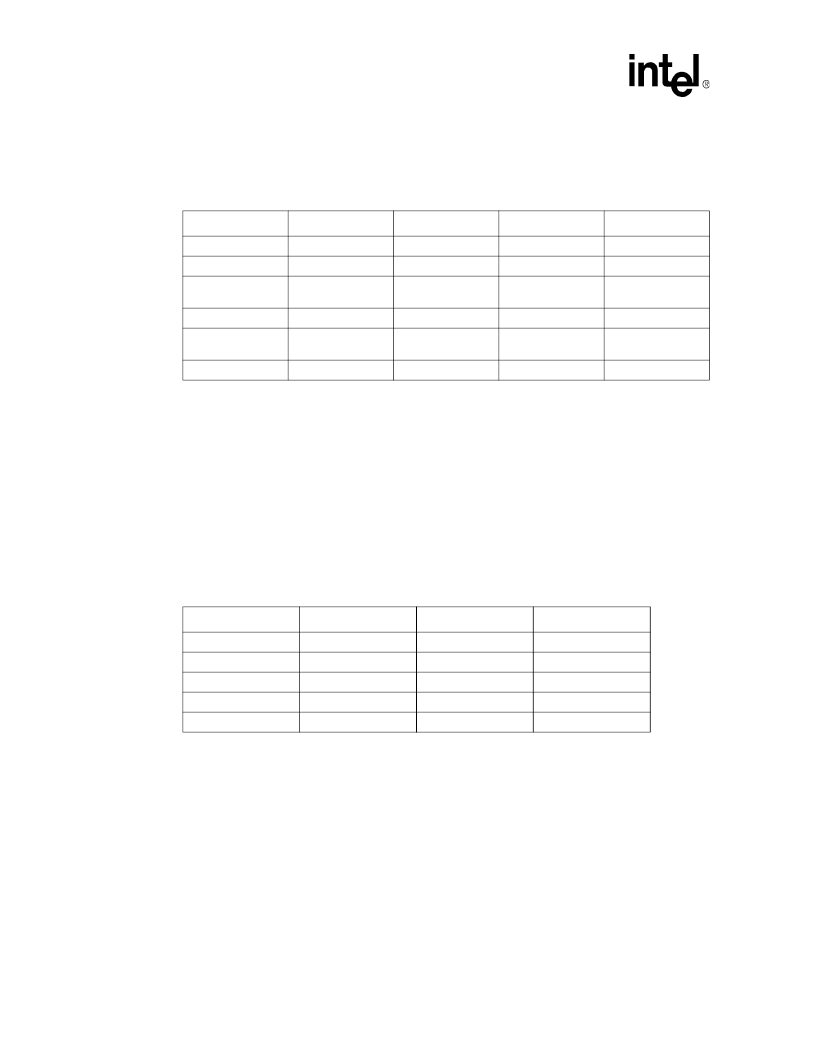

4.2.2

Type 2 Driver DC Specifications

Table 36

refers to pin types: I2, O2.

Note:

In

Table 35

and

Table 36

, currents into the chip (chip sinking) are denoted as positive(+) current.

Currents from the chip (chip sourcing) are denoted as negative(-) current. Input leakage currents

include high-Z output leakage for all bidirectional buffers with tri-state outputs. The electrical

specifications are preliminary and subject to change.

4.2.3

Overshoot/Undershoot Specifications

The IXP1250 has been designed to be tolerant of overshoot and undershoot associated with normal

I/O switching. However, excessive overshoot or undershoot of I/O signals can cause the device to

latchup.

Table 37

specifies limits on I/O overshoot and undershoot that should never be exceeded.

Table 36. I2 and O2 Pin Types

Symbol

Parameter

Condition

Minimum

Maximum

V

ih

Input High Voltage

0.5 x VDDX

VDD_REF + 0.5 V

V

il

Input Low Voltage

---

0.3 x VDDX

V

oh

Output High

Voltage

Ioh = -500 uA

0.9 x VDDX

---

V

ol

Output Low Voltage

Iol = 1500 uA

---

0.1 x VDDX

I

i

Input Leakage

Current

1

1. Input leakage currents include high impedance output leakage for all bidirectional buffers with tri-state outputs.

0

≤

Vin

≤

VDDX

-10

μ

A

10

μ

A

C

in

Pin Capacitance

5 pF

10 pF

Table 37. Overshoot/Undershoot Specifications

Pin Type

Undershoot

Overshoot

Maximum Duration

I1/O1

-0.75 V

VDDX + 0.7 V

4 ns

I2/O2

-0.7 V

VDDX + 0.65 V

4 ns

O3

-0.7 V

VDDX + 0.6 V

4 ns

O4

-0.75 V

VDDX + 1.0 V

4 ns

O5

-0.7 V

VDDX + 0.65 V

4 ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCIXP1250-232 | Microprocessor |

| GCK101 | Analog IC |

| GCK131 | Microcontroller |

| GCM-3.15A | Fuse |

| GCM-4A | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GCIXP1250BA | 功能描述:IC MPU NETWORK 166MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BB | 功能描述:IC MPU NETWORK 200MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BC | 功能描述:IC MPU NETWORK 232MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCJ0335C5C0JR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

| GCJ0335C5C1AR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。