- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67592 > FUSION878A (CONEXANT SYSTEMS) COLOR SIGNAL DECODER, PQFP128 PDF資料下載

參數(shù)資料

| 型號: | FUSION878A |

| 廠商: | CONEXANT SYSTEMS |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL DECODER, PQFP128 |

| 封裝: | PLASTIC, QFP-128 |

| 文件頁數(shù): | 5/180頁 |

| 文件大?。?/td> | 2067K |

| 代理商: | FUSION878A |

第1頁第2頁第3頁第4頁當前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁

3.0 Electrical Interfaces

Fusion 878A

3.3 General Purpose I/O Port

PCI Video Decoder

3-18

Conexant

100600B

3.3.7 Digital Video Input Mode

The GPIO port can be configured to accept general digital data streams. The parts

contain a TG_RAM-based state machine that isolates the digital video input

events from the internal decoder timing. This allows the digital video input H and

V events to synchronize the sequencer, and allows the programmable output

events to be positioned where needed to synchronize the decoder.

The digital input port provides flexibility for interfacing to various video

standards. Software for programming the parts is included in the development kit

for interfacing to the supported video standards. Table 3-5 provides the alternate

pin definitions when using the digital video-in mode. Additional digital interfaces

may be implemented by changing the TG_RAM contents. Contact your local

Conexant sales office for more information.

3.3.7.1 CCIR656

CCIR656 is a 27 MBps interface in the form of Cb, Y, Cr, Y, Cb, etc. In this

sequence, the word sequence Cb, Y, Cr, refers to co-sited and color-difference

samples, and the following word, Y, corresponds to the next luminance sample.

In this interface, two timing reference codes, SAV and EAV occur at the start

and end of active video, respectively. These 4-byte codes occur at the outside

boundaries of the active video. In the active video line, 720 pixels correspond to

1440 samples; 1448 bytes comprise a video data block (one line of video with

reference codes).

The full video line consists of 1716 bytes (in 525 line systems) and 1728 bytes

(in 625 line systems). The line breaks into two parts. The first part is blanking,

which consists of the front porch, HSYNC, back porch, and 276 bytes (288 in 635

line systems) from EAV through SAV. The leading edge of HSYNC occurs

32-bytes (24 in 625 line systems) after the start of the digital line. The field

interval is aligned to this leading edge of HSYNC.

Figure 3-12 illustrates a diagram of the interface. For a full reference on this

standard, please refer to the International Telecommunications Union (ITU)

specification, ITU-R-BT656. This can be obtained from the ITU Web Site at

http://www.itu.int/publications/.

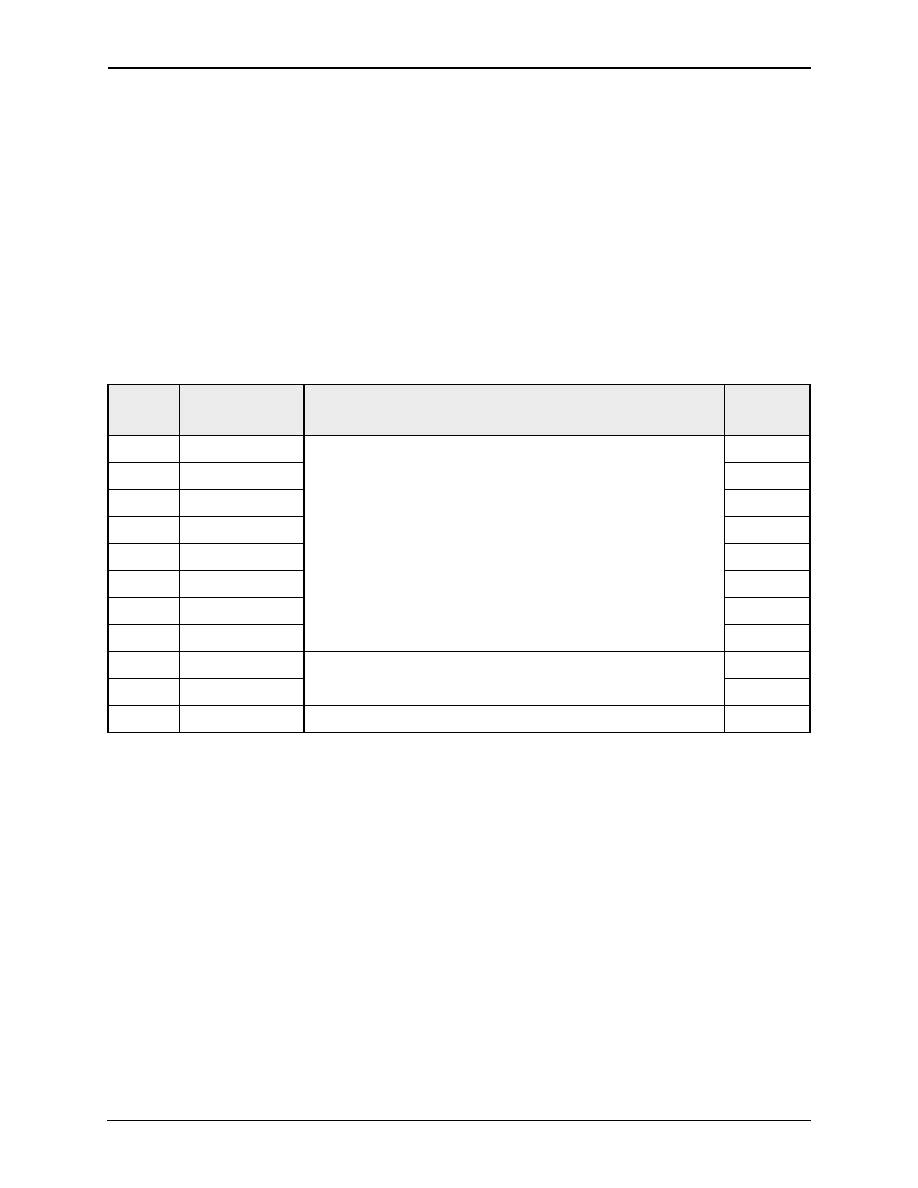

Table 3-5. Pin Definition of GPIO Port When Using Digital Video-In Mode

GPIO

Signal

Description

Pin

Number

[23]

CLKx1

Output signals for synchronizing to input video.

56

[22]

FIELD

57

[21]

VACTIVE

58

[20]

VSYNC

59

[19]

HACTIVE

60

[18]

HSYNC

61

[17]

Composite ACTIVE

67

[16]

Composite SYNC

68

[20]

VSYNC/FIELD

Input signals for synchronizing to input video.

59

[18]

HSYNC

61

[7:0]

DATA

Cb0, Y0, Cr0, Y1 ... Video data input at GPCLK = CLK × 2 rate.

79–86

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FVXO-HC53BR-FREQ | VCXO, CLOCK, 0.75 MHz - 250 MHz, HCMOS OUTPUT |

| FVXO-HC72BR-FREQ | VCXO, CLOCK, 0.75 MHz - 180 MHz, HCMOS OUTPUT |

| FVXO-HC73B-FREQ | VCXO, CLOCK, 0.75 MHz - 250 MHz, HCMOS OUTPUT |

| FVXO-LC52BR-FREQ | VCXO, CLOCK, 0.75 MHz - 1000 MHz, LVDS OUTPUT |

| FVXO-LC72BR-FREQ | VCXO, CLOCK, 0.75 MHz - 1000 MHz, LVDS OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FUSZ03 | 制造商:Honeywell Sensing and Control 功能描述: |

| FUTURE 1AA PLUS | 制造商:Ansmann 功能描述: 制造商:ANSMANN AG 功能描述: |

| FUTURE 2AA PLUS | 制造商:Ansmann 功能描述: 制造商:ANSMANN AG 功能描述: |

| FUTURE 2C PLUS | 制造商:Ansmann 功能描述: 制造商:ANSMANN AG 功能描述: |

| FUTURE 3D PLUS | 制造商:Ansmann 功能描述: 制造商:ANSMANN AG 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。