- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄295865 > E28F320J5-120 (INTEL CORP) StrataFlash MEMORY TECHNOLOGY 32 AND 64 MBIT PDF資料下載

參數(shù)資料

| 型號: | E28F320J5-120 |

| 廠商: | INTEL CORP |

| 元件分類: | PROM |

| 英文描述: | StrataFlash MEMORY TECHNOLOGY 32 AND 64 MBIT |

| 中文描述: | 2M X 16 FLASH 5V PROM, 150 ns, PDSO56 |

| 封裝: | 14 X 20 MM, TSOP-56 |

| 文件頁數(shù): | 50/51頁 |

| 文件大小: | 651K |

| 代理商: | E28F320J5-120 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁當(dāng)前第50頁第51頁

28F320J5 and 28F640J5

8

Datasheet

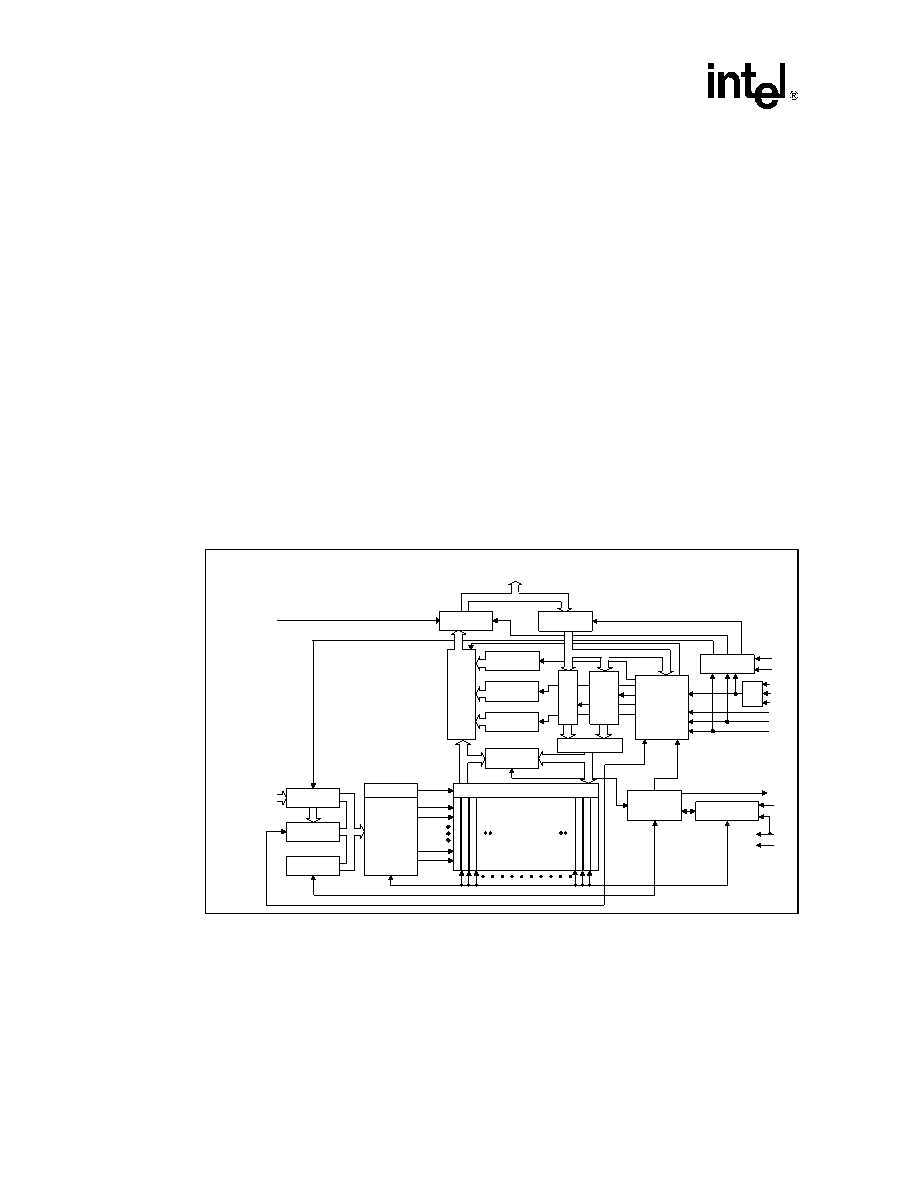

Three CE pins are used to enable and disable the device. A unique CE logic design (see Table 2,

“Chip Enable Truth Table” on page 12) reduces decoder logic typically required for multi-chip

designs. External logic is not required when designing a single chip, a dual chip, or a 4-chip

miniature card or SIMM module.

The BYTE# pin allows either x8 or x16 read/writes to the device. BYTE# at logic low selects 8-bit

mode; address A0 selects between the low byte and high byte. BYTE# at logic high enables 16-bit

operation; address A1 becomes the lowest order address and address A0 is not used (don’t care). A

device block diagram is shown in Figure 1.

is enabled. When the RP# pin is at GND, a further power-down mode is enabled which minimizes

power consumption and provides write protection during reset. A reset time (tPHQV) is required

from RP# switching high until outputs are valid. Likewise, the device has a wake time (tPHWL)

from RP#-high until writes to the CUI are recognized. With RP# at GND, the WSM is reset and the

status register is cleared.

The Intel StrataFlash memory devices are available in several package types. The 64-Mbit is

available in 56-lead SSOP (Shrink Small Outline Package) and BGA* package (micro Ball Grid

Array). The 32-Mbit is available in 56-lead TSOP (Thin Small Outline Package) and 56-lead

SSOP. Figures 2, 3, and 4 show the pinouts.

Figure 1. Intel StrataFlash Memory Block Diagram

32-Mbit: Thirty-two

64-Mbit: Sixty-four

128-Kbyte Blocks

Input Buffer

Ou

tp

u

t

Mult

iplexer

Y-Gating

Program/Erase

Voltage Switch

Data

Comparator

Status

Register

Identifier

Register

Da

ta

Re

gi

s

te

r

I/O Logic

Address

Latch

Address

Counter

X-Decoder

Y-Decoder

Input Buffer

Output Buffer

GND

V

CC

V

PEN

CE

0

CE

1

CE

2

WE#

OE#

RP#

BYTE#

Command

User

Interface

32-Mbit: A

0-A21

64-Mbit: A

0- A22

DQ

0 -DQ15

V

CC

W

ri

te

B

u

ffer

Write State

Machine

Multiplexer

Query

STS

V

CCQ

CE

Logic

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| E28F400BX-B120 | 4-MBIT (256K X 16, 512K X 8) BOOT BLOCK FLASH MEMORY FAMILY |

| E28F400BX-B60 | ACTUATOR, SWITCH, ROUND, MOMENTARY; Approval Bodies:BEAB, VDE, UL, CSA; Diameter, external:29mm; IP rating:65; Operations, mechanical No. of:1000000; Temp, op. max:85(degree C); Temp, op. min:-20(degree C) RoHS Compliant: Yes |

| E28F400BX-B80 | 4-MBIT (256K X 16, 512K X 8) BOOT BLOCK FLASH MEMORY FAMILY |

| E28F400BX-T120 | 4-MBIT (256K X 16, 512K X 8) BOOT BLOCK FLASH MEMORY FAMILY |

| E28F004BX-T120 | OSC 5V SMT PLAS 14X9 CMOS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| E28F320J5A-120 | 制造商:Intel 功能描述: |

| E28F320S5-110 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| E28F320S5-90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:WORD-WIDE FlashFile MEMORY FAMILY |

| E28F400B5B60 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 5 BOOT BLOCK FLASH MEMORY FAMILY 2, 4, 8 MBIT |

| E28F400B5B80 | 制造商:Rochester Electronics LLC 功能描述: 制造商:Intel 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。