- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378216 > 82557 (Intel Corp.) Fast Ethernet PCI Bus Controller(快速以太網(wǎng) PCI總線控制器) PDF資料下載

參數(shù)資料

| 型號: | 82557 |

| 廠商: | Intel Corp. |

| 英文描述: | Fast Ethernet PCI Bus Controller(快速以太網(wǎng) PCI總線控制器) |

| 中文描述: | 快速以太網(wǎng)PCI總線控制器(快速以太網(wǎng)的PCI總線控制器) |

| 文件頁數(shù): | 21/57頁 |

| 文件大小: | 601K |

| 代理商: | 82557 |

INTEL 82557 FAST ETHERNET PCI BUS CONTROLLER

21

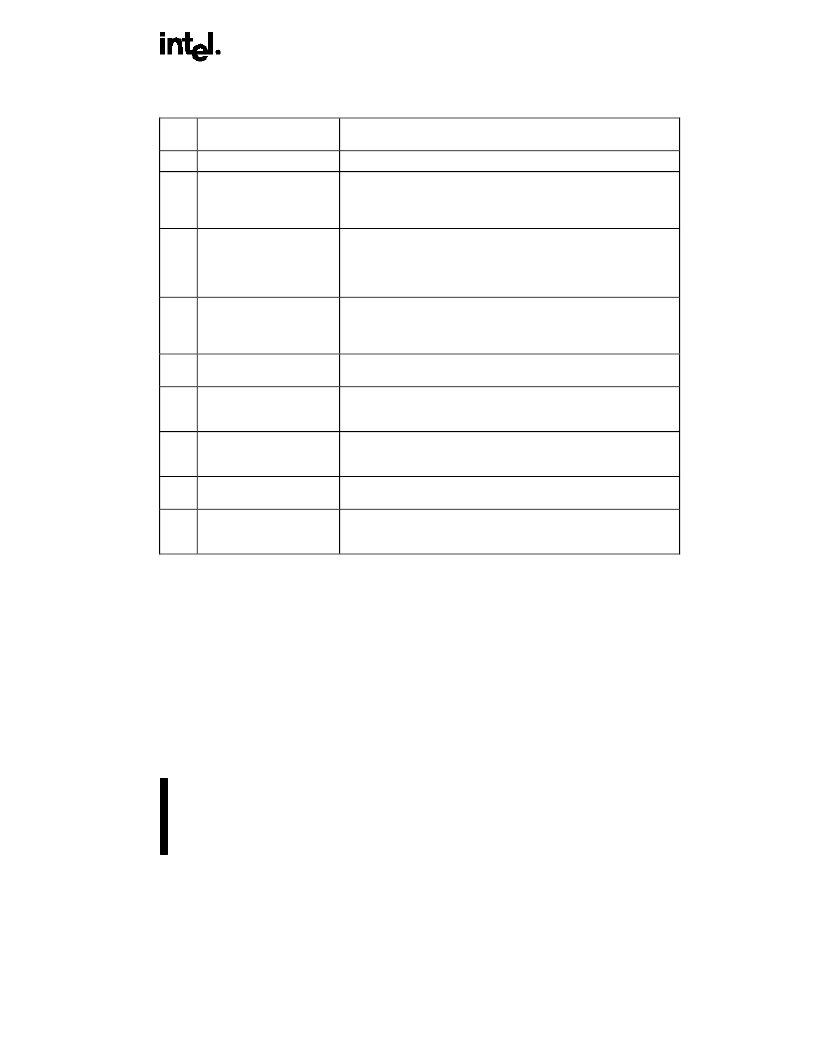

Table 4. PCI Status Register Bits

Bit #

Bit Location

Description

0-6

Reserved

These bits are hardwired to 0 in the 82557.

7

Fast Back to Back Capable

This read-only bit indicates whether or not the target is capable of

accepting fast back-to-back transactions when the transactions are not

to the same agent. The value of this bit in the 82557 is 1 (Fast Back to

Back Capable).

8

Data Parity Detected

This bit is set when three conditions are met: 1) the bus agent asserted

PERR# itself or observed PERR# asserted; 2) the agent setting the bit

acted as the bus master for the operation in which the error occurred; 3)

the Parity Error Response bit (Command Register) is set. The initial

value of this bit in the 82557 is 0.

9-10

DEVSEL# Timing

These bits encode the timing of DEVSEL#. There are three allowable

timings for assertion of DEVSEL#. These are encoded as 00b for fast,

01b for medium, and 10b for slow (11b is reserved). The value of these

bits are always set to 01 (medium).

11

Signaled Target Abort

This bit must be set by a target device whenever it terminates a

transaction with target-abort. The value of this bit is always 0.

12

Received Target Abort

This bit must be set by a master device whenever its transaction is

terminated with target-abort. The initial value of this bit in the 82557 is

0.

13

Received MasterAbort

This bit must be set by a master device whenever its transaction

(except for Special Cycle) is terminated with master-abort. The initial

value of this bit in the 82557 is 0.

14

Signaled SystemError

This bit must be set whenever the device asserts SERR#. The initial

value of this bit in the 82557 is 0.

15

Detected Parity Error

This bit must be set by the device whenever it detects a parity error,

even if parity error handling is disabled (as controlled by bit 6 in the

Command register). The initial value of this bit in the 82557 is 0.

Miscellaneous PCI Configuration Registers

This section describes the registers that are device

independent and only need to be implemented by

devices that provide the described function. The

specific implementation of each register for the

82557 is provided in Table 5.

相關PDF資料 |

PDF描述 |

|---|---|

| 82559 | Fast Ethernet Multifunction PCI/CARD bus controller(快速以太網(wǎng)多功能PCI/CARD 總線控制器) |

| 8255A-5 | PROGRAMMABLE PERIPHEAL INTERFACE |

| 8255A | IC LOGIC 3257 4-BIT 1-OF-2 FET MULTIPLEXER/DEMULTIPLEXER -40+85C SSOP-16 - OBSOLETE |

| 8255A | Programmable Peripheral Interface iAPX86 Family |

| 8255A-5 | 12-Bit, 2.7 V to 5.25 V, 1.5 MSPS Low Power ADC; Package: SOIC - Wide; No of Pins: 24; Temperature Range: Industrial |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 8255702-025 | 制造商:ITT Interconnect Solutions 功能描述:NASA CONNECTOR - Bulk |

| 8255702-095 | 制造商:ITT Interconnect Solutions 功能描述:NASA CONNECTOR - Bulk |

| 8255702-096 | 制造商:ITT Interconnect Solutions 功能描述:NASA CONNECTOR - Bulk |

| 8255702-098 | 制造商:ITT Interconnect Solutions 功能描述:NASA CONNECTOR - Bulk |

| 8255704-050 | 制造商:ITT Interconnect Solutions 功能描述:NASA CONNECTOR - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。