- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370035 > 28233-11 (CONEXANT SYSTEMS) ATM Transmitter/Receiver with UTOPIA Interface PDF資料下載

參數(shù)資料

| 型號: | 28233-11 |

| 廠商: | CONEXANT SYSTEMS |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM Transmitter/Receiver with UTOPIA Interface |

| 中文描述: | TRANSCEIVER, PQFP160 |

| 封裝: | PLASTIC, MQFP-160 |

| 文件頁數(shù): | 117/161頁 |

| 文件大小: | 1832K |

| 代理商: | 28233-11 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁當(dāng)前第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

CN8223

3.0 Registers

ATM Transmitter/Receiver with UTOPIA Interface

3.7 Status Register Overview

100046C

Conexant

3-31

Set when PLCP OOF is active for eight consecutive PLCP frames. Not used in direct mapping

mode.

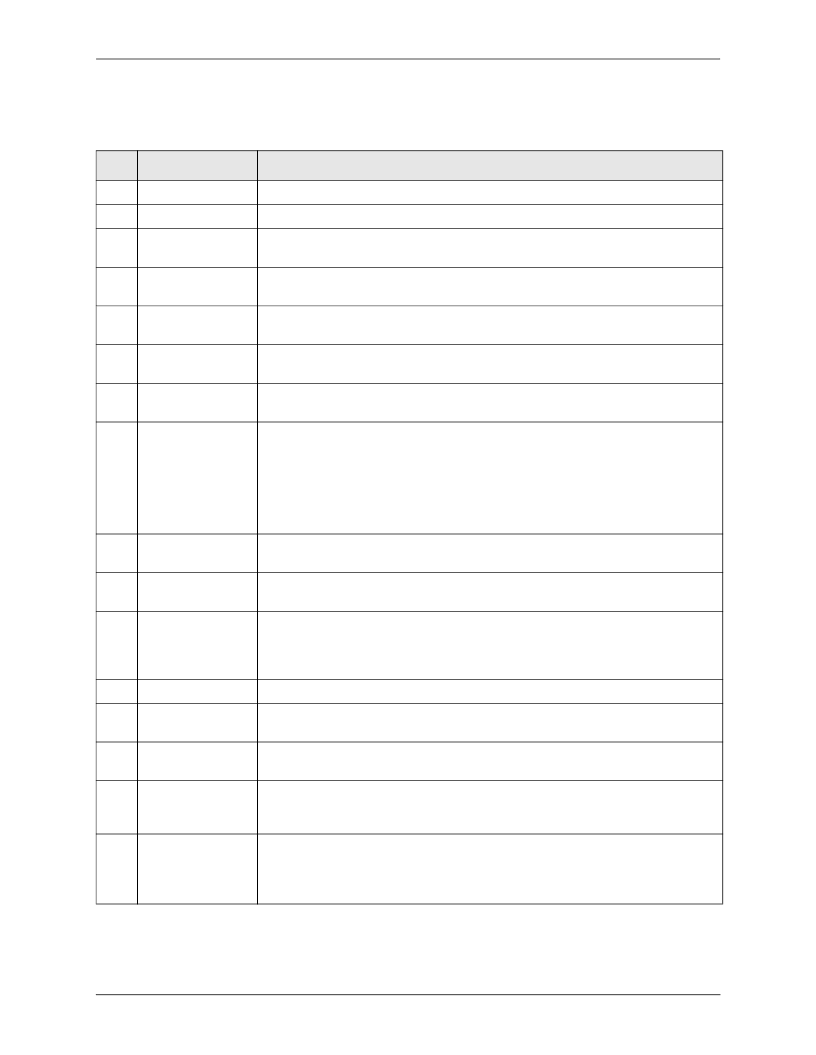

Table 3-13

provides definitions for the DS3 PLCP and Direct Mapping Mode LINE_STATUS bits.

Table 3-13. DS3 PLCP and Direct Mapping Mode LINE_STATUS Bit Definitions

Bit

Name

Description

15

0

Not used

14

One-Second Count

Set if the one-second timer input is detected.

13

PLCP Invalid FEBE

Set if an invalid FEBE is detected (9

–

F) in the G1 octet in 57-octet PLCP formats. Not used in

direct mapping mode.

12

PLCP FEBE All-1s

Set if an invalid FEBE = F is detected in the G1 octet in 57-octet PLCP formats. Not used in

direct mapping mode.

11

PLCP FEBE Error

Set if any valid non-0 FEBE value (values 0x1

–

0x8) is detected in the G1 octet in 57-octet PLCP

formats. Not used in direct mapping mode.

10

PLCP BIP Error

Set if there is an error in the BIP-8 code (B1 octet) checking in 57-octet PLCP formats. Not

used in Direct Mapping mode.

9

PLCP Frame Error

Set if there is an error in either the A1 or A2 octets of the PLCP frame pattern for 57-octet

PLCP formats. Not used in direct mapping mode.

8

PLCP Yellow/LOC

In PLCP mode, PLCP yellow indicates that the yellow alarm bit in the G1 octet (57-octet

modes) has been active for 10 consecutive PLCP frames. This bit will also be active for

57-octet formats using external framers or the parallel interface.

In Direct Mapping mode, LOC indicates that HEC cell delineation has been lost. Cell

delineation is lost if seven consecutive HEC errors occur at the current cell delineation

position.This bit will be active for 53-octet formats using external framers or the parallel

interface. (This bit is functionally redundant with bit 5 when configured in this mode).

7

PLCP LOF 2

–

3

Set if PLCP LOF is high for three consecutive one-second latching signals (rising edge on

ONESECI). Not used in direct mapping mode.

6

PLCP LOF

5

PLCP OOF/LOC

Set if the PLCP OOF state has been entered for 57-octet PLCP formats. In direct mapping

mode, it indicates that HEC cell delineation has been lost. Cell delineation is lost if seven

consecutive HEC errors occur at the current cell delineation position. (This bit is functionally

redundant with bit 8 when configured in Direct Mapping mode.)

4

DS3 X-bit Yellow

Set if the internal DS3 framer detects both X1 and X2 low in an M-frame.

3

DS3 Idle Code

Indicates that the internal DS3 framer has detected an idle code signal. A DS3 idle code is a

1100... payload with valid framing and parity, equal X bits, and all subframe 3 C bits set to 0.

2

DS3 AIS

Indicates that the internal DS3 framer has detected an AIS. A DS3 AIS is a 1010... payload with

valid framing and parity, equal X bits, and all C bits set to 0.

1

DS3 OOF

Indicates that the internal DS3 framer has lost frame alignment. An OOF condition for DS3

occurs when 3 out of 16 F bits are in error, or 2 out of 3 M-frames contain M bit errors.

Reframe time is typically 1 ms.

0

LOS (Input)

Set if there is a LOS detected by the internal B3ZS/HDB3 decoder, or if the RXLOS~ input pin is

active low. Internal LOS detection is the occurrence of 175

±

75 zeros prior to B3ZS/HDB3

decoding. The RXLOS~ input pin (RXIN[4]) should be tied high unless an external line

interface unit provides an active low LOS indication.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28C010TRPDB-12 | 150 x 32 pixel format, LED Backlight available |

| 28C010TRT1DE-15 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1DE-20 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1FB-15 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1FB-20 | 1 Megabit (128K x 8-Bit) EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 282332-2 | 制造商:TE Connectivity 功能描述: |

| 282-333 | 制造商:WAGO Innovative Connections 功能描述:END PLATE RAIL MOUNTED TERMINAL BLOCK 制造商:WAGO 功能描述:END PLATE, RAIL MOUNTED TERMINAL BLOCK 制造商:WAGO Innovative Connections 功能描述:END PLATE, RAIL MOUNTED TERMINAL BLOCK; Series:282; Accessory Type:End Plate; For Use With:Rail Mounted Terminal Blocks; Color:Orange; Mounting Type:DIN Rail ;RoHS Compliant: Yes |

| 2823337 | 功能描述:工業(yè)繼電器 ST-REL4-KG120/21-21 RoHS:否 制造商:TE Connectivity / Kilovac 觸點(diǎn)形式:1 Form A (SPST-NO) 觸點(diǎn)電流額定值: 線圈電壓:9 VDC to 36 VDC 線圈電阻:38 Ohms 線圈電流: 切換電壓: 安裝風(fēng)格:Panel 觸點(diǎn)材料:Silver Palladium |

| 282-334 | 制造商:WAGO Innovative Connections 功能描述:End Plate 2 mm Thick-Color Grey For Use With Rail Mounted Terminal Block 制造商:WAGO 功能描述:GREY END PLATE 制造商:WAGO Innovative Connections 功能描述:END PLATE, 2MM, GREY; Series:-; Accessory Type:End Plate; For Use With:Rail Mounted Terminal Blocks ;RoHS Compliant: Yes |

| 282-334 | 制造商:WAGO Innovative Connections 功能描述:END PLATE 制造商:WAGO 功能描述:END PLATE |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。