- 您現(xiàn)在的位置:買賣IC網 > PDF目錄382783 > μPD30102 (NEC Corp.) 64-/32-BIT Microprocessor(64/32位微處理器) PDF資料下載

參數(shù)資料

| 型號: | μPD30102 |

| 廠商: | NEC Corp. |

| 英文描述: | 64-/32-BIT Microprocessor(64/32位微處理器) |

| 中文描述: | 64-/32-BIT微處理器(64/32位微處理器) |

| 文件頁數(shù): | 73/112頁 |

| 文件大小: | 639K |

| 代理商: | ΜPD30102 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁當前第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

μ

PD30102

73

Preliminary Data Sheet

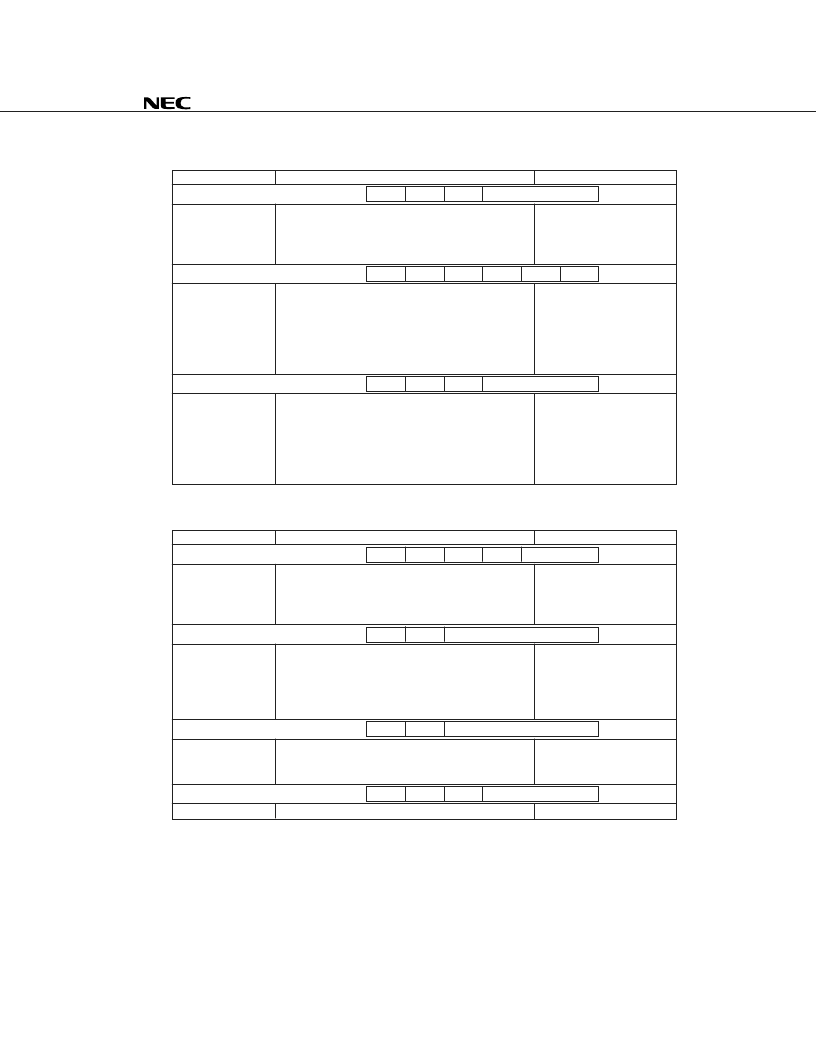

Table 22-2. CPU Instruction Set: Extended ISA (2/2)

Instruction

Description

Format

Branch instruction (2)

REGIMM

rs

sub

offset

BLTZL

Branch On Less Than Zero Likely

BLTZL

rs, offset

BGEZL

Branch On Greater Than Or Equal To Zero Likely

BGEZL

rs, offset

BLTZALL

Branch On Less Than Zero And Link Likely

BLTZALL rs, offset

BGEZALL

Branch On Greater Than Or Equal To Zero And Link Likely

BGEZALL rs, offset

Exception instruction

SPECIAL

rs

rt

rd

sa

funct

TGE

Trap If Greater Than Or Equal

TGE

rs, rt

TGEU

Trap If Greater Than Or Equal Unsigned

TGEU

rs, rt

TLT

Trap If Less Than

TLT

rs, rt

TLTU

Trap If Less Than Unsigned

TLTU

rs, rt

TEQ

Trap If Equal

TEQ

rs, rt

TNE

Trap If Not Equal

TNE

rs, rt

Exception immediate instruction

REGIMM

rs

sub

immediate

TGEI

Trap If Greater Than Or Equal Immediate

TGEI

rs, immediate

TGEIU

Trap If Greater Than Or Equal Immediate Unsigned

TGEIU

rs, immediate

TLTI

Trap If Less Than Immediate

TLTI

rs, immediate

TLTIU

Trap If Less Than Immediate Unsigned

TLTIU

rs, immediate

TEQI

Trap If Equal Immediate

TEQI

rs, immediate

TNEI

Trap If Not Equal Immediate

TNEI

rs, immediate

Table 22-3. System Control Coprocessor (CP0) Instruction Set

Instruction

Description

Format

System control coprocessor instruction (1)

COP0

sub

rt

rd

0

MFC0

Move From Coprocessor 0

MFC0

rt, rd

MTC0

Move To Coprocessor 0

MTC0

rt, rd

DMFC0

Doubleword Move From Coprocessor 0

DMFC0

rt, rd

DMTC0

Doubleword Move To Coprocessor 0

DMTC0

rt, rd

System control coprocessor instruction (2)

COP0

CO

funct

TLBR

Read Indexed TLB Entry

TLBR

TLBWI

Write Indexed TLB Entry

TLBWI

TLBWR

Write Random TLB Entry

TLBWR

TLBP

Probe TLB For Matching Entry

TLBP

ERET

Exception Return

ERET

System control coprocessor instruction (3)

COP0

CO

funct

STANDBY

Standby

STANDBY

SUSPEND

Suspend

SUSPEND

HIBERNATE

Hibernate

HIBERNATE

System control coprocessor instruction (4)

CACHE

base

sub

offset

CACHE

Cache Operation

CACHE

sub, offset (base)

相關PDF資料 |

PDF描述 |

|---|---|

| μPD30121 | 64-Bit MIPS RISC Microprocessor(64 位RISC 微處理器) |

| μPD30122 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30181 | 64-Bit RISC Microprosessor(64位RISC微處理器) |

| μPD30210 | 64-Bit MIPS RISC Microprocessor(64位MIPS RISC 微處理器) |

| μPD30200 | High-Performance, 64-Bit RISC Microprosessor(高性能64位RISC微處理器) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| PD301-024-03-PC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| PD301-024-03-P-C-200 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-250 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-P-C-300 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:DC to DC Converter |

| PD301-024-03-PI | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購,3分鐘左右您將得到回復。