- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367733 > P83CL882 (NXP Semiconductors N.V.) 80C51 Ultra Low Power ULP telephony controller PDF資料下載

參數(shù)資料

| 型號(hào): | P83CL882 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 80C51 Ultra Low Power ULP telephony controller |

| 中文描述: | 80C51的超低功耗無鉛汽油電話控制器 |

| 文件頁數(shù): | 61/88頁 |

| 文件大小: | 328K |

| 代理商: | P83CL882 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

2001 Jun 19

61

Philips Semiconductors

Product specification

80C51 Ultra Low Power (ULP) telephony controller

P83CL882

6.9.6

W

AVEFORM GENERATION WITH

MOUT[2:0]

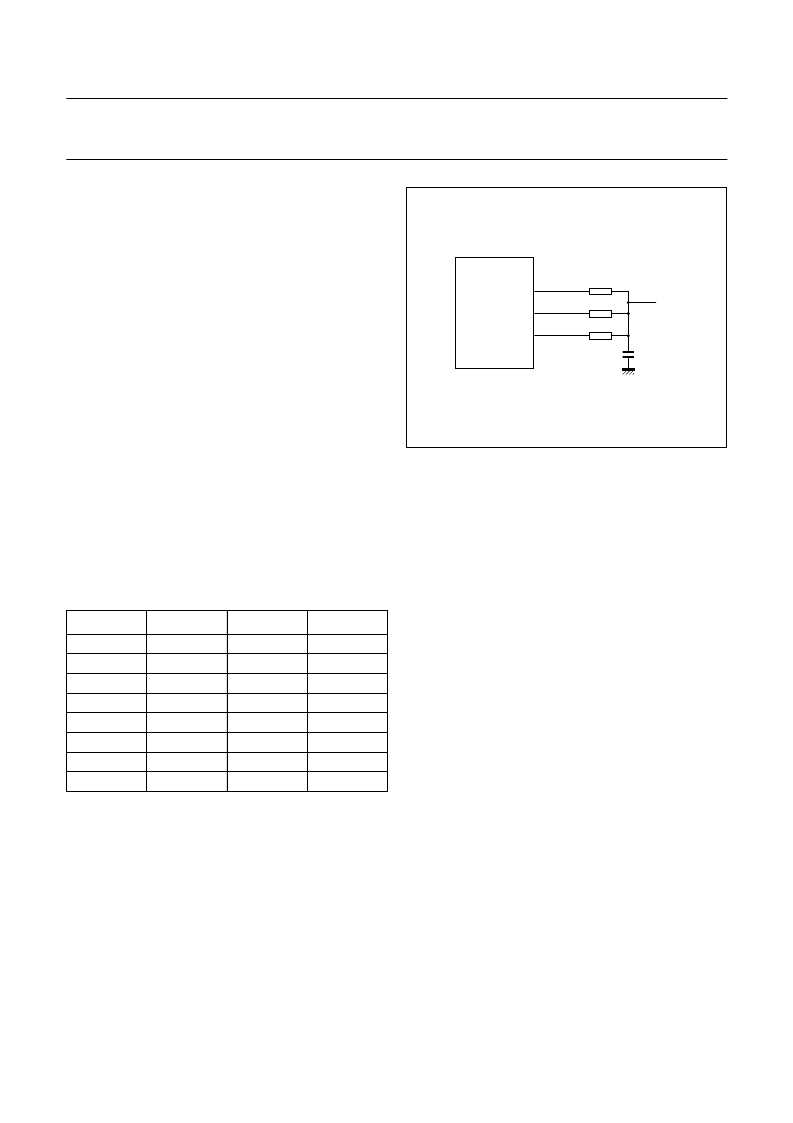

The 3 digital output pins MOUT0 to MOUT2, should be

used as an input to a 3-bit external DAC. The signals can

be connected via external resistors R0, R1 and R2 to

a summation point and then be filtered with an external

capacitor (C1). The 3-bit DAC is shown in Fig.29. Table 76

gives the relationship between the MOUT pins and VOUT.

Figure 30 shows the waveforms that are produced by the

waveform generator. The horizontal axis shows the

sample counter on which the waveform changes its value.

Each bit is built-up out of 2

×

124 samples.

The vertical axis shows the values of MOUT[2:0], forming

the inputs of the resistive DAC. The first half of the

waveform is determined by the previous and the current

bit,whereasthesecondhalfofthewaveformisdetermined

by the current and the next bit to be transmitted. The count

frequency of the sample counter depends on the

programmed baud rate.

If the transmitter is disabled with MTEN set to a logic 0,

MOUT[2:0] is ‘111’ to save power in the resistive DAC.

If the transmitter is enabled and no data is transmitted,

MOUT[2:0] has an idle value of ‘100’, which corresponds

to 0.57V

DD

.

Table 76

VOUT as a function of MOUT[2:0]

Note

1.

VOUT with resistor values (see Fig.29): R1 = 0.5R0;

R2 = 0.25R0

6.9.7

M

ANCHESTER CODING OF DATA

The bits of the data byte written in MBUF are Manchester

encoded as shown in Fig.30. A logic 1 is coded as

a LOW-to-HIGH transition in the middle of a bitcell,

a logic 0 is coded as a HIGH-to-LOW transition.The

Manchester encoded signal contains redundancy for early

error detection in received bits. A non-matching

HIGH-to-LOW or LOW-to-HIGH pair indicates an error

condition.The Manchester encoded signal has a polarity

change in each bitcell.

MOUT2

MOUT1

MOUT0

VOUT

(1)

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

0.14V

DD

0.29V

DD

0.43V

DD

0.57V

DD

0.71V

DD

0.86V

DD

V

DD

handbook, halfpage

MGK231

WAVEFORM

GENERATOR

MOUT0

MOUT1

MOUT2

R0

R1

R2

VOUT

C1 = 10 nF

Fig.29 3-bit DAC with MOUT[2:0].

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83CL883T | TELX microcontrollers for CT0 handset/basestation applications |

| P83CL884T | TELX microcontrollers for CT0 handset/basestation applications |

| P87CL883T | TELX microcontrollers for CT0 handset/basestation applications |

| P87CL884T | TELX microcontrollers for CT0 handset/basestation applications |

| P8503BMG | N-Channel Logic Level Enhancement Mode Field Effect Transistor (Preliminary) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83CL882T/001 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 Ultra Low Power ULP telephony controller |

| P83CL883T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:TELX microcontrollers for CT0 handset/basestation applications |

| P83CL883T/XXX | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|SOP|28PIN|PLASTIC |

| P83CL884T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:TELX microcontrollers for CT0 handset/basestation applications |

| P83CL884T/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。