- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄367733 > P83CL882 (NXP Semiconductors N.V.) 80C51 Ultra Low Power ULP telephony controller PDF資料下載

參數(shù)資料

| 型號: | P83CL882 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 80C51 Ultra Low Power ULP telephony controller |

| 中文描述: | 80C51的超低功耗無鉛汽油電話控制器 |

| 文件頁數(shù): | 6/88頁 |

| 文件大?。?/td> | 328K |

| 代理商: | P83CL882 |

第1頁第2頁第3頁第4頁第5頁當(dāng)前第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

2001 Jun 19

6

Philips Semiconductors

Product specification

80C51 Ultra Low Power (ULP) telephony controller

P83CL882

5.2

Pin description

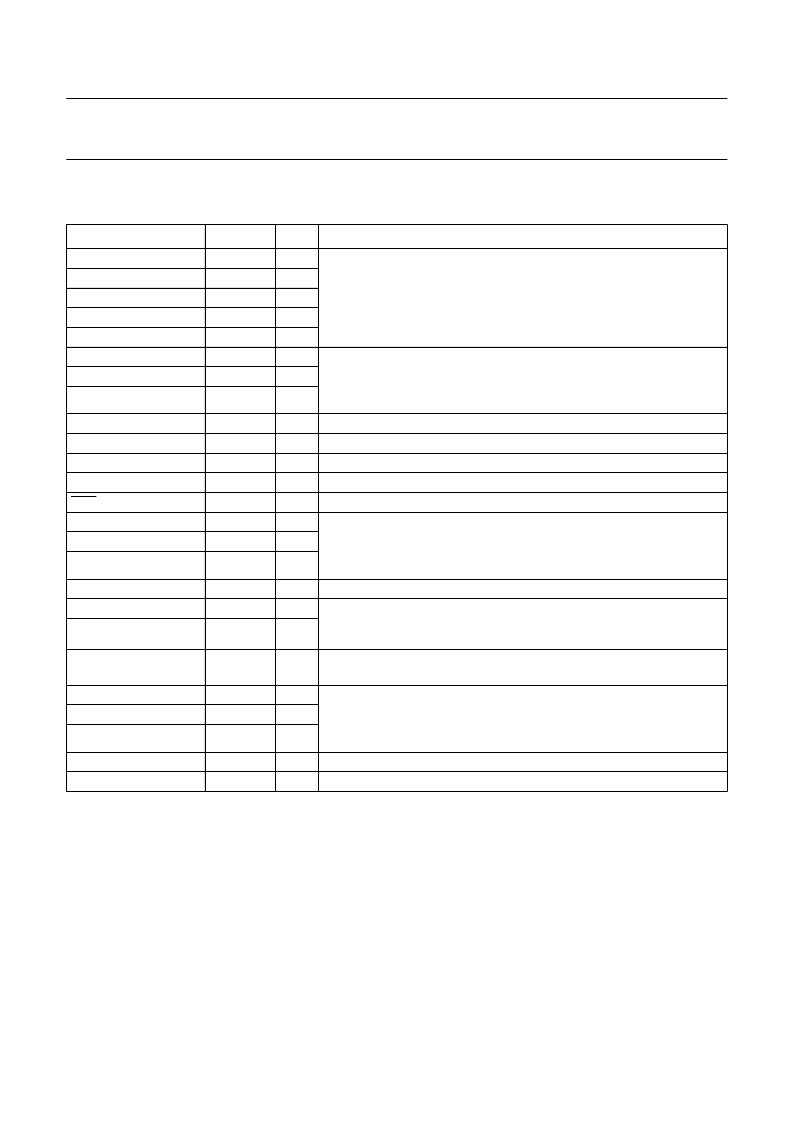

Table 1

Pin description for TSSOP32 (SOT487-1)

Note

1.

For high current drive capability on I/Os all supply pins should be connected.

SYMBOL

PIN

TYPE

DESCRIPTION

P3.3

P3.4/T0

P3.5/T1

P3.6

P3.7

P1.2/INT4/T2

P1.1/INT3/T2EX

P1.0/INT2

1

2

3

4

5

6

7

8

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

Port 3: P3.3 to P3.7; bidirectional I/O port with two alternative functions.

P3.4 also serves as the Timer 0 external count input (T0). P3.5 also

serves as the Timer 1 external count input (T1).

Port 1: P1.2 to P1.0; bidirectional I/O port with alternative functions.

INT4, INT3 and INT2 are the external interrupts 4, 3 and 2 respectively.

P1.2 also serves as Timer 2 input (T2). P1.1 also serves as Timer 2

external input (T2EX).

ground

power supply voltage

crystal output

crystal input; external clock input

reset input/output pin; active LOW

Port 3: P3.0 to P3.2; bidirectional I/O port with alternative functions.

MOUT2 to MOUT0 are the MSK outputs (mapped on the lower 3 bits of

Port 3). P3.2 also serves as the external interrupt 0 input (INT1)

and P3.1 as the external interrupt 1 input (INT0).

MSK input

Port 1: P1.6 and P1.7; can only be used as open-drain output or

high-impedance input. Alternative functions: INT8 and INT9, external

interrupt 8 and 9. SCL and SDA I

2

C-bus interface clock and data.

Port 0: 8-bit bidirectional I/O port. Every port pin can be used as

open-drain, standard port, high-impedance input or push-pull output.

Port 1: P1.3 to P1.5; bidirectional I/O port with alternative functions

INT5, INT6 and INT7: external interrupt 5 to 7. P1.4 also serves as

auxiliary clock output (CLKOUT). P1.5 also serves as the Timer 2 output

(T2OUT).

periphery (I/O) positive supply voltage

periphery (I/O) ground

V

SS(1)

V

DD(1)

XTAL2

XTAL1

RST

P3.0/MOUT0

P3.1/MOUT1/INT1

P3.2/MOUT2/INT0

9

10

11

12

13

14

15

16

S

S

O

I

I/O

I/O

I/O

I/O

MIN

P1.6/INT8/SCL

P1.7/INT9/SDA

17

18

19

I

I/O

I/O

P0.0 to P0.7

20 to 27

I/O

P1.3/INT5

P1.4/INT6/CLKOUT

P1.5/INT7/T2OUT

28

29

30

I/O

I/O

I/O

V

DDP(1)

V

SSP(1)

31

32

S

S

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| P83CL883T | TELX microcontrollers for CT0 handset/basestation applications |

| P83CL884T | TELX microcontrollers for CT0 handset/basestation applications |

| P87CL883T | TELX microcontrollers for CT0 handset/basestation applications |

| P87CL884T | TELX microcontrollers for CT0 handset/basestation applications |

| P8503BMG | N-Channel Logic Level Enhancement Mode Field Effect Transistor (Preliminary) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P83CL882T/001 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:80C51 Ultra Low Power ULP telephony controller |

| P83CL883T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:TELX microcontrollers for CT0 handset/basestation applications |

| P83CL883T/XXX | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:MICROCONTROLLER|8-BIT|8051 CPU|CMOS|SOP|28PIN|PLASTIC |

| P83CL884T | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:TELX microcontrollers for CT0 handset/basestation applications |

| P83CL884T/XXX | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:8-Bit Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。