- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄369830 > LQ80221 LAN Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | LQ80221 |

| 英文描述: | LAN Transceiver |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器 |

| 文件頁(yè)數(shù): | 53/91頁(yè) |

| 文件大小: | 907K |

| 代理商: | LQ80221 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)當(dāng)前第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)

80220/80221

4-53

MD400159/E

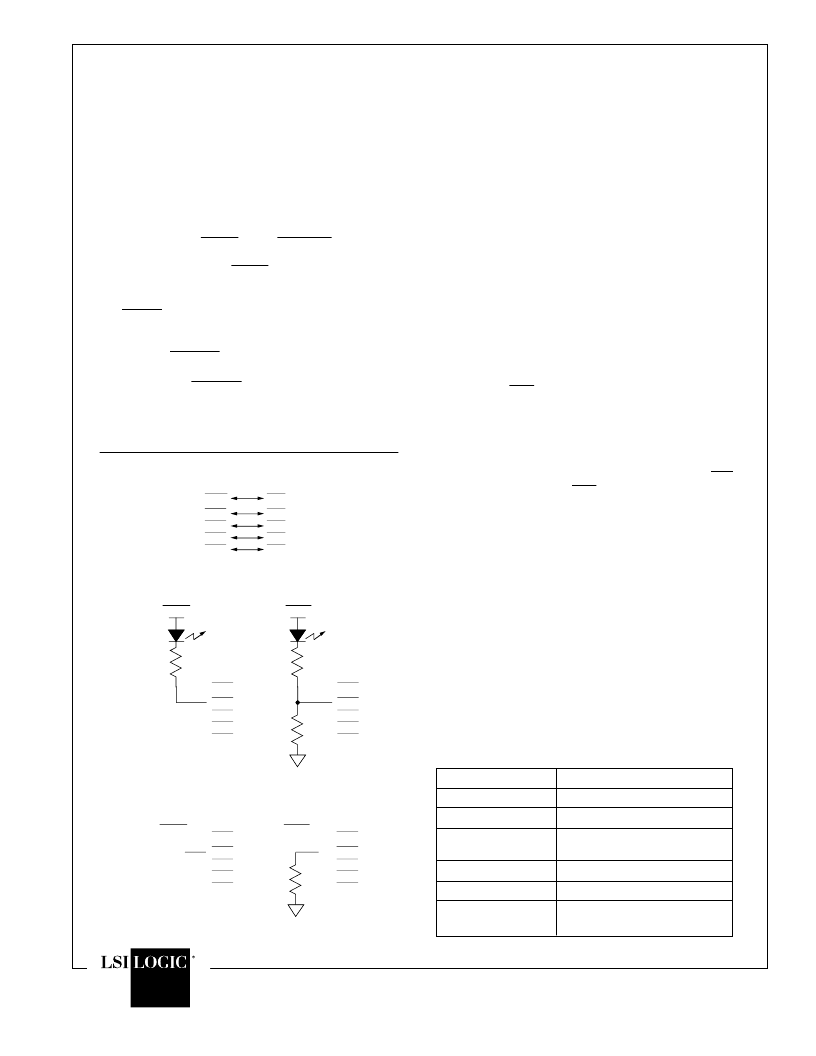

the address s desired, then a 50K resistor to GND must be

added as shown in Figure 15b.

If no LED's are needed on the LED outputs, the selection

of addresses can be done as shown n Figure 15c. If a high

address is desired, the pin should be left floating and the

internal pullup will pull the pin high during power-on reset

time and latch in a high address value. If a low address is

desired, then the MDINT and PLED[3:0] output pins

should be tied either directly o GND or hrough an optional

50K resistor to GND. PLED3 should always be tied

through a 50K resistor to GND since t has both pullup and

pulldown capability. The optional 50K resistor also allows

the MDINT and PLED[2:0] pins to be used as digital

outputs under normal conditions.

Note that the MDA[4:0] addresses are inverted inside the

80220/80221 before going to the MI serial port block. This

means that the MDA[4:0] pins would have to be pin

strapped to 11111 externally in order to successfully

match the MI physical address bits PHYAD[4:0]=00000

internally.

Figure 15. Serial Device Port Address Selection

5.11 LONG CABLE

IEEE 802.3 specifies that 10BaseT and 100BaseTX oper-

ate over twisted pair cable lengths of between 0-100

meters. The squelch evels can be reduced by 4.5 dB f the

receive level adjust bit is appropriately set in the MI serial

port Configuration 1 register, which will allow the 80220/

80221 to operate with up to 150 meters of twisted pair

cable. The equalizer s already designed to accommodate

between 0-125 meters of cable.

5.12 AUTOMATIC JAM

The 80220/80221 has an automatic JAM generation fea-

ture which automatically transmits a JAM packet when

receive activity is detected. This feature is primarily de-

signed to give the user a means to easily implement half

duplex flow control. In a typical application, a watermark

signal from a system FIFO or memory would be tied

directly to the JAM pin. When the system FIFO is nearly

full and more data s ncoming rom receiver, he device will

automatically transmit a JAM packet and create a collision

which will cause the far end device to backoff allowing time

for the system FIFO to empty itself.

The JAM generation eature requires hat he RX_EN/JAM

pin be programmed for JAM. This can be done by

appropriately setting the R/J configuration select bit in the

MI serial port Configuration 2 register.

5.13 OSCILLATOR

The 80220/80221 requires a 25 Mhz reference frequency

for internal signal generation. This 25 Mhz reference

frequency can be generated by either connecting an

external 25 Mhz crystal between OSCIN and GND or by

applying an external 25 Mhz clock to OSCIN.

If the crystal oscillator is used, it needs only a crystal, and

no other external capacitors or other components are

required. The crystal must have the characteristics shown

in Table 24. The crystal must be placed as close as

possible to OSCIN and GND pins so that parasitics on

OSCIN are kept to a minimum.

Table 24. Crystal Specifications

Parameter

Type

Frequency

Equivalent Series

Resistance

Load Capacitance

Case Capacitance

Power

Dissipation

Spec

Parallel Resonant

25 Mhz +/- 0.01%

25 ohms max

18 pF typ

7 pF max

1mW max

a.) OUTPUT DRIVER / INPUT ADDRESS CORRESPONDENCE

b.) SETTING ADDRESS WITH LEDs

500

500

50 K

HIGH

LOW

c.) SETTING ADDRESS WITHOUT LEDs

HIGH

LOW

FLOAT

PLED3

PLED2

PLED1

PLED0

MDINT

PLED3

PLED2

PLED1

PLED0

MDINT

PLED3

PLED2

PLED1

PLED0

PLED3

PLED2

PLED1

PLED0

MDA3

MDA2

MDA1

MDA0

PLED3

PLED2

PLED1

PLED0

MDINT

MDA4

MDINT

(OPT)

MDINT

50K

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LQT100X | Peripheral IC |

| LQT1KX | Peripheral IC |

| LQT50X3 | Peripheral IC |

| LQT60X3 | Peripheral IC |

| LQV3M2768-3CGR | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LQ821 | 制造商:POLYFET 制造商全稱(chēng):Polyfet RF Devices 功能描述:SILICON GATE ENHANCEMENT MODE RF POWER LDMOS TRANSISTOR |

| LQ9D161 | 制造商:SHARP 制造商全稱(chēng):Sharp Electrionic Components 功能描述:DEVICE SPECIFICATION FOR TFT-LCD module |

| LQ9D340 | 制造商:SHARP 制造商全稱(chēng):Sharp Electrionic Components 功能描述:Color TFT-LCD Module for Measuring instruments/Banking terminals |

| LQA03TC600 | 功能描述:整流器 Q-Series 600V 3A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

| LQA05TC600 | 功能描述:整流器 Q-Series 600V 5A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。