- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369830 > LQ80221 LAN Transceiver PDF資料下載

參數(shù)資料

| 型號: | LQ80221 |

| 英文描述: | LAN Transceiver |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器 |

| 文件頁數(shù): | 5/91頁 |

| 文件大小: | 907K |

| 代理商: | LQ80221 |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁

80220/80221

4-5

MD400159/E

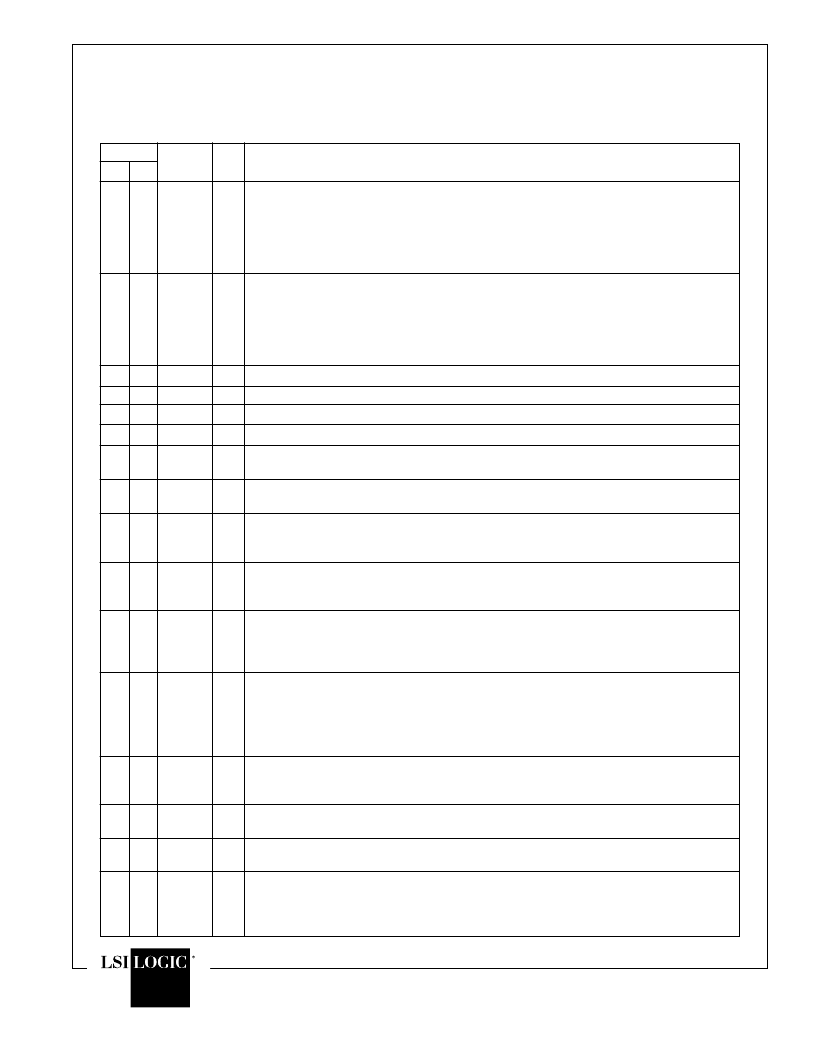

Pin#

44L 64L

28

24

11

10

1

44

27

23

36

9

4

41

42

43

2

3

40

Pin

Name

I/O

Description

32

25

8

7

57

56

31

23

41

6

60

52

54

55

58

59

50

VCC6

VCC5

VCC4

VCC3

VCC2

VCC1

GND6

GND5

GND4

GND3

GND2

GND1

TPO+

TPO -

TPI+

TPI -

REXT

—

Positive Supply.

5

±

5% Volts

—

Ground.

0 Volts

O

O

I

I

—

Twisted Pair Transmit Output, Positive.

Twisted Pair Transmit Output, Negative.

Twisted Pair Receive Input, Positive.

Twisted Pair Receive Input, Negative.

Transmit Current Set.

An external resistor connected between this pin and GND will set the

output current level for the twisted pair outputs.

Clock Oscillator Input.

There must be either a 25 Mhz crystal between this pin and GND or

a 25 Mhz clock applied to this pin. TX_CLK output is generated from this input.

Transmit Clock Output.

This controller interface output provides a clock to an external

controller. Transmit data from the controller on TXD, TX_EN, and TX_ER is clocked in on

rising edges of TX_CLK and OSCIN.

Transmit Enable Input.

This controller interface input has to be asserted active high to

indicate that data on TXD and TX_ER is valid, and it is clocked in on rising edges of TX_CLK

and OSCIN.

Transmit Data Input.

These controller interface inputs contain input nibble data to be

transmitted on the TP outputs, and they are clocked in on rising edges of TX_CLK and OSCIN

when TX_EN is asserted.

37

42

OSCIN

I

29

34

TX_CLK

O

35

40

TX_EN

I

33

32

31

30

34

38

37

36

35

39

TXD3

TXD2

TXD1

TXD0

TX_ER /

TXD4

I

I

Transmit Error Input.

This controller interface input causes a special pattern to be

transmitted on the twisted pair outputs in place of normal data, and it is clocked in on rising

edges of TX_CLK when TX_EN is asserted.

If the device is placed in the Bypass 4B5B Encoder mode, this pin is reconfigured to be the

fifth TXD transmit data input, TXD4.

Receive Clock Output.

This controller interface output provides a clock to an external

controller. Receive data on RXD, RX_DV, and RX_ER is clocked out on falling edges of

RX_CLK.

Carrier Sense Output.

This controller interface output is asserted active high when valid data

is detected on the receive twisted pair inputs, and it is clocked out on falling edges of RX_CLK.

Receive Data Valid Output.

This controller interface output is asserted active high when valid

decoded data is present on the RXD outputs, and it is clocked out on falling edges of RX_CLK.

Receive Data Output.

These controller interface outputs contain receive nibble data from

the TP input, and they are clocked out on falling edges of RX_CLK.

25

26

RX_CLK

O

16

13

CRS

O

17

14

RX_DV

O

19

20

21

22

19

20

21

22

RXD3

RXD2

RXD1

RXD0

O

1.0 Pin Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LQT100X | Peripheral IC |

| LQT1KX | Peripheral IC |

| LQT50X3 | Peripheral IC |

| LQT60X3 | Peripheral IC |

| LQV3M2768-3CGR | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LQ821 | 制造商:POLYFET 制造商全稱:Polyfet RF Devices 功能描述:SILICON GATE ENHANCEMENT MODE RF POWER LDMOS TRANSISTOR |

| LQ9D161 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:DEVICE SPECIFICATION FOR TFT-LCD module |

| LQ9D340 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:Color TFT-LCD Module for Measuring instruments/Banking terminals |

| LQA03TC600 | 功能描述:整流器 Q-Series 600V 3A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

| LQA05TC600 | 功能描述:整流器 Q-Series 600V 5A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。