- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369830 > LQ80221 LAN Transceiver PDF資料下載

參數(shù)資料

| 型號(hào): | LQ80221 |

| 英文描述: | LAN Transceiver |

| 中文描述: | 網(wǎng)絡(luò)收發(fā)器 |

| 文件頁(yè)數(shù): | 12/91頁(yè) |

| 文件大小: | 907K |

| 代理商: | LQ80221 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)

80220/80221

MD400159/E

12

On the receive side for 100 Mbps operation, the twisted

pair receiver receives incoming encoded and scrambled

MLT-3 data from the twisted pair cable, remove any high

frequency noise, equalizes the nput signal to compensate

for he effects of he cable, qualifies he data with a squelch

algorithm, and converts he data rom MLT-3 coded wisted

pair levels to internal digital levels. The output of the

twisted pair receiver then goes to a clock and data recov-

ery block which recovers a clock from the incoming data,

uses the clock to latch in valid data into the device, and

converts the data back to NRZ format. The NRZ data is

then unscrambled and decoded by the 4B5B decoder and

descrambler, respectively, and outputted to an external

Ethernet controller by the controller interface.

10 Mbps operation is similar to the 100 Mbps operation

except, (1) there is no scrambler/descrambler, (2) the

encoder/decoder is Manchester instead of 4B5B, (3) the

data rate is 10 Mbps instead of 100 Mbps, and (4) the

twisted pair symbol data is two level Manchester instead

of ternary MLT-3.

The AutoNegotiation block automatically configures the

device for either 100Base-TX or 10Base-T, and for either

Full or Half Duplex. This configuration is based on the

capabilities selected for this device and the capabilities

detected from a remote device.

The Management Interface, (hereafter referred to as the

MI serial port), s a two pin bidirectional ink through which

configuration inputs can be set and status outputs can be

read.

Each block plus the operating modes are described in

more detail in the following sections. Since the 80220/

80221 can operate either as a 100Base-TX or a 10Base-T

device, each of he ollowing sections describes he perfor-

mance of the respective section in both the 100 and 10

Mbps modes.

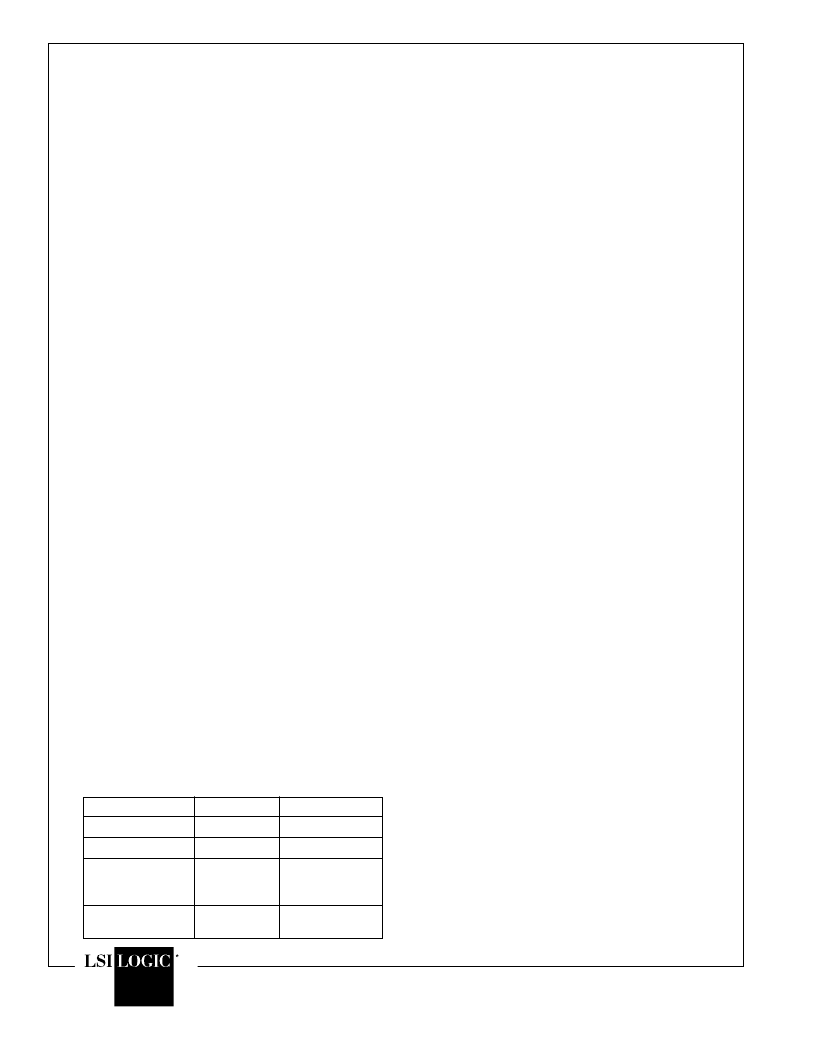

3.2 DIFFERENCES BETWEEN 80220 AND 80221

The differences between the 80220 and 80221 are sum-

marized n Table 1. For more nformation on each of these

features, refer to the appropriate sections where these

features are described.

Table 1. 80220 vs. 80221

80220

44L PLCC

# LED Outputs

External

100Base-T4

Interface

Repeater Mode

Pin

Feature

Package

80221

64L LQFP

6

Yes

4

No

No

Yes

3.3 CONTROLLER INTERFACE

3.3.1 General

The 80220/80221 has two interfaces to an external con-

troller: Media Independent Interface (referred to as the

MII) and Five Bit interface (referred to as the FBI).

3.3.2 MII - 100 Mbps

The MII is a nibble wide packet data interface defined in

IEEE 802.3 and shown in Figure 3. The 80220/80221

meets all he MII requirements outlined n EEE 802.3. The

80220/80221 can directly connect, without any external

logic, to any Ethernet controllers or other devices which

also complies with the IEEE 802.3 MII specifications. The

MII frame format is shown in Figure 3.

The MII consists of eighteen signals: four transmit data

bits (TXD[3:0]), transmit clock (TX_CLK), transmit enable

(TX_EN), transmit error (TX_ER), four receive data bits

(RXD[3:0]), receive clock (RX_CLK), carrier sense (CRS),

receive data valid (RX_DV), receive data error (RX_ER),

and collision (COL). The transmit and receive clocks

operate at 25 MHz in 100 Mbps mode.

On the transmit side, the TX_CLK output runs continu-

ously at 25 Mhz. When no data s o be ransmitted, TX_EN

has o be deasserted. While TX_EN s deasserted, TX_ER

and TXD[3:0] are ignored and no data is clocked into the

device. When TX_EN is asserted on the rising edge of

TX_CLK, data on TXD[3:0] is clocked into the device on

rising edges of the TX_CLK output clock. TXD[3:0] input

data is nibble wide packet data whose format needs to be

the same as specified in IEEE 802.3 and shown in Figure

3. When all data on TXD[3:0] has been latched into the

device, TX_EN has to be deasserted on the rising edge of

TX_CLK.

TX_ER is also clocked in on rising edges of the TX_CLK

clock. TX_ER is a transmit error signal which, when

asserted, will substitute an error nibble in place of the

normal data nibble that was clocked in on TXD[3:0]. The

error nibble s defined to be the /H/ symbol which s defined

in IEEE 802.3 and shown in Table 2.

Since OSCIN input clock generates the TX_CLK output

clock, TXD[3:0], TX_EN, and TX_ER are also clocked in

on rising edges of OSCIN.

On the receive side, as long as a valid data packet is not

detected, CRS and RX_DV are deasserted and RXD[3:0]

is held ow. When the start of packet s detected , CRS and

RX_DV are asserted on falling edge of RX_CLK. The

assertion of RX_DV ndicates hat valid data is clocked out

on RXD[3:0] on falling edges of the RX_CLK clock. The

RXD[3:0] data has he same rame structure as he TXD[3:0]

data and s specified n IEEE 802.3 and shown n Figure 3.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LQT100X | Peripheral IC |

| LQT1KX | Peripheral IC |

| LQT50X3 | Peripheral IC |

| LQT60X3 | Peripheral IC |

| LQV3M2768-3CGR | Peripheral IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LQ821 | 制造商:POLYFET 制造商全稱:Polyfet RF Devices 功能描述:SILICON GATE ENHANCEMENT MODE RF POWER LDMOS TRANSISTOR |

| LQ9D161 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:DEVICE SPECIFICATION FOR TFT-LCD module |

| LQ9D340 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:Color TFT-LCD Module for Measuring instruments/Banking terminals |

| LQA03TC600 | 功能描述:整流器 Q-Series 600V 3A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

| LQA05TC600 | 功能描述:整流器 Q-Series 600V 5A Ultra Low Qrr RoHS:否 制造商:Vishay Semiconductors 產(chǎn)品:Standard Recovery Rectifiers 配置: 反向電壓:100 V 正向電壓下降: 恢復(fù)時(shí)間:1.2 us 正向連續(xù)電流:2 A 最大浪涌電流:35 A 反向電流 IR:5 uA 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DO-221AC 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。