- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄24828 > 935268625551 (NXP SEMICONDUCTORS) UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 935268625551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類(lèi): | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁(yè)數(shù): | 36/82頁(yè) |

| 文件大小: | 1965K |

| 代理商: | 935268625551 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

Philips Semiconductors

ISP1581

Hi-Speed USB interface device

Product data

Rev. 05 — 26 February 2003

41 of 78

9397 750 10766

Koninklijke Philips Electronics N.V. 2003. All rights reserved.

9.4.9

DMA Endpoint register (address: 58H)

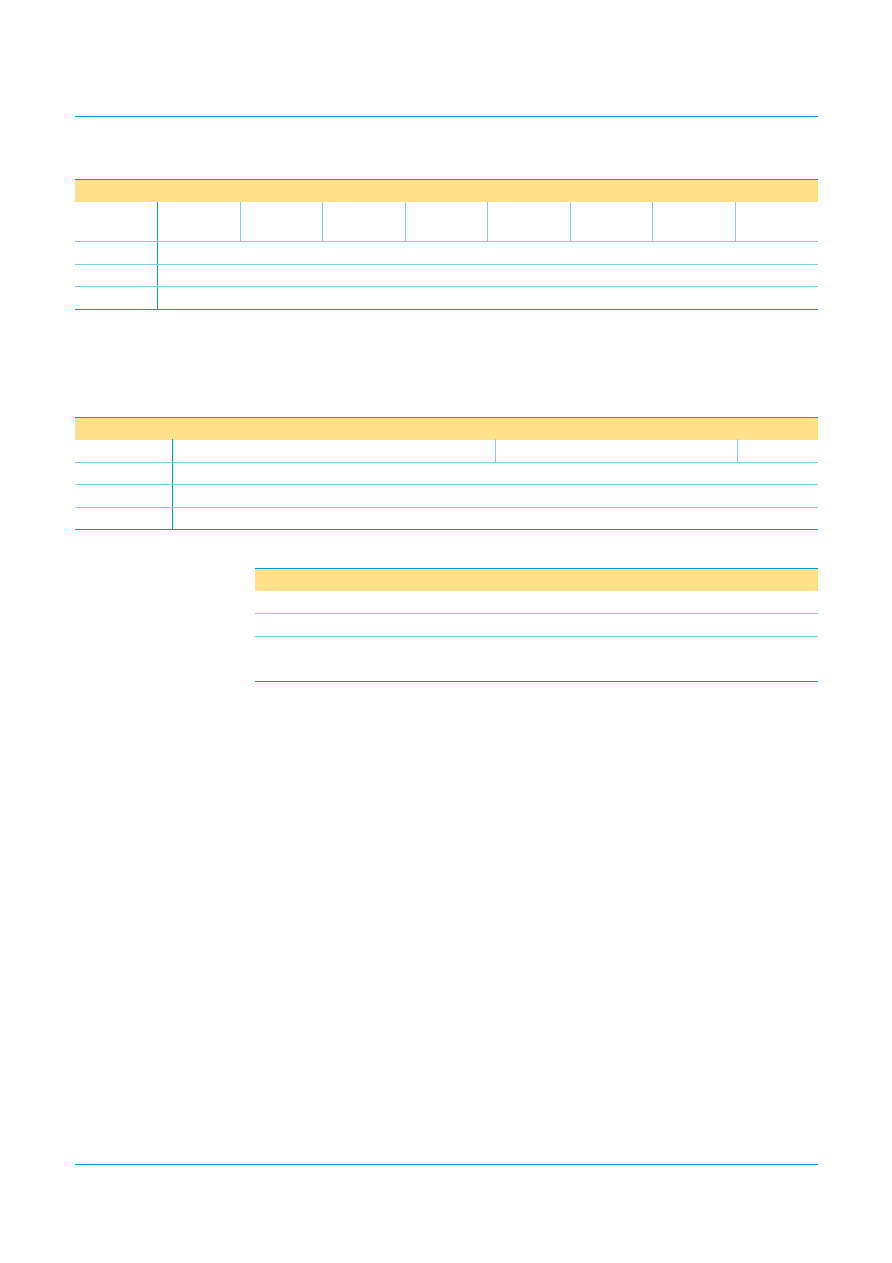

This 1-byte register selects a USB endpoint FIFO as a source or destination for DMA

transfers. The bit allocation is given in Table 55.

The DMA Endpoint register must not reference the endpoint that is indexed by the

Endpoint Index register (02CH) at any time. Doing so would result in data corruption.

Therefore, if the DMA Endpoint register is unused, point it to an unused endpoint.

However, if the DMA Endpoint register is pointed to an active endpoint, the rmware

must not reference the same endpoint on the Endpoint Index register.

9.5 General registers

9.5.1

Interrupt register (address: 18H)

The Interrupt register consists of 4 bytes. The bit allocation is given in Table 57.

When a bit is set in the Interrupt register, this indicates that the hardware condition for

an interrupt has occurred. When the Interrupt register content is non-zero, the INT

output will be asserted. Upon detecting the interrupt, the external microprocessor

must read the Interrupt register to determine the source of the interrupt.

Each endpoint buffer has a dedicated interrupt bit (EPnTX, EPnRX). In addition,

various bus states can generate an interrupt: Resume, Suspend, Pseudo-SOF, SOF

and Bus Reset. The DMA Controller only has one interrupt bit: the source for a DMA

interrupt is shown in the DMA Interrupt Reason register (see Table 51).

Each interrupt bit can be individually cleared by writing a logic 1. The DMA interrupt

bit can be cleared by writing a logic 1 to the related interrupt source bit in the DMA

Interrupt Reason register and writing a logic 1 to the DMA bit of the interrupt register.

Bit

7

6

5

4

3

2

1

0

Symbol

IE_1F0_

WF_E

IE_1F0_

WF_F

IE_1F0_

RF_E

IE_

READ_1F0

IE_BSY_

DONE

IE_TF_

RD_DONE

IE_CMD_

INTRQ_OK

reserved

Reset

0000000

-

Bus reset

0000000

-

Access

R/W

Table 55:

DMA Endpoint register: bit allocation

Bit

7

6

5

4

3

2

1

0

Symbol

reserved

EPIDX[2:0]

DMADIR

Power Reset

----

0000

Bus Reset

----

0000

Access

R/W

Table 56:

DMA Endpoint register: bit description

Bit

Symbol

Description

7 to 4

-

reserved

3 to 1

EPIDX[2:0]

selects the indicated endpoint for DMA access

0

DMADIR

0 — selects the RX/OUT FIFO for DMA read transfers

1 — selects the TX/IN FIFO for DMA write transfers.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 080207R0 | TELEFON-AKKU |

| 080216R0 | TELEFON-AKKU |

| 080219R0 | TELEFON-AKKU |

| 080251R0 | TELEFON-AKKU |

| 935268664112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。