- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄24828 > 935268625551 (NXP SEMICONDUCTORS) UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 PDF資料下載

參數(shù)資料

| 型號(hào): | 935268625551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 總線控制器 |

| 英文描述: | UNIVERSAL SERIAL BUS CONTROLLER, PQFP64 |

| 封裝: | 10 X 10 MM, 1.40 MM HEIGHT, PLASTIC, MS-026, SOT-314-2, LQFP-64 |

| 文件頁(yè)數(shù): | 25/82頁(yè) |

| 文件大?。?/td> | 1965K |

| 代理商: | 935268625551 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

Philips Semiconductors

ISP1581

Hi-Speed USB interface device

Product data

Rev. 05 — 26 February 2003

31 of 78

9397 750 10766

Koninklijke Philips Electronics N.V. 2003. All rights reserved.

[1]

PIO Read or Write that started using DMA Command Register only performs 16-bit transfer.

9.4.2

DMA Transfer Counter register (address: 34H)

This 4-byte register is used to set up the total byte count of a DMA transfer (DMACR).

It indicates the remaining number of bytes left for transfer. The bit allocation is given

in Table 31.

The transfer counter is used in DMA modes: PIO (commands: 04H, 05H), UDMA

(commands: 02H, 03H), MDMA (commands: 06H, 07H) and GDMA (commands:

00H, 01H).

A new value is written into the register starting with the lower byte (DMACR1) or the

lower word (MSByte: DMACR2, LSByte: DMACR1). Internally, the transfer counter is

initialized only after the last byte (DMACR4) has been written.

In the GDMA Slave mode only, the transfer counter can be disabled via bit

DIS_XFER_CNT in the DMA Conguration Register (see Table 33). In this case,

input signal EOT can be used to terminate the DMA transfer when data is transferred

from the external device to the host via IN tokens. The last packet in the FIFO is

validated when pin EOT is asserted.

11

Reset DMA

Reset DMA: Initializes the DMA core to its power-on

reset state.

Remark: When the DMA core is reset during the Reset

DMA command, the DREQ, DACK, DIOW and DIOR

handshake pins will be temporarily asserted. This can

cause some confusion to the external DMA Controller.

To prevent this from happening, start the external DMA

Controller only after the DMA reset is done.

12

MDMA stop

MDMA stop: This command immediately stops the

MDMA data transfer. This is applicable for commands

06H and 07H only.

13 to FF

-

reserved

Table 30:

DMA commands…continued

Code (Hex)

Name

Description

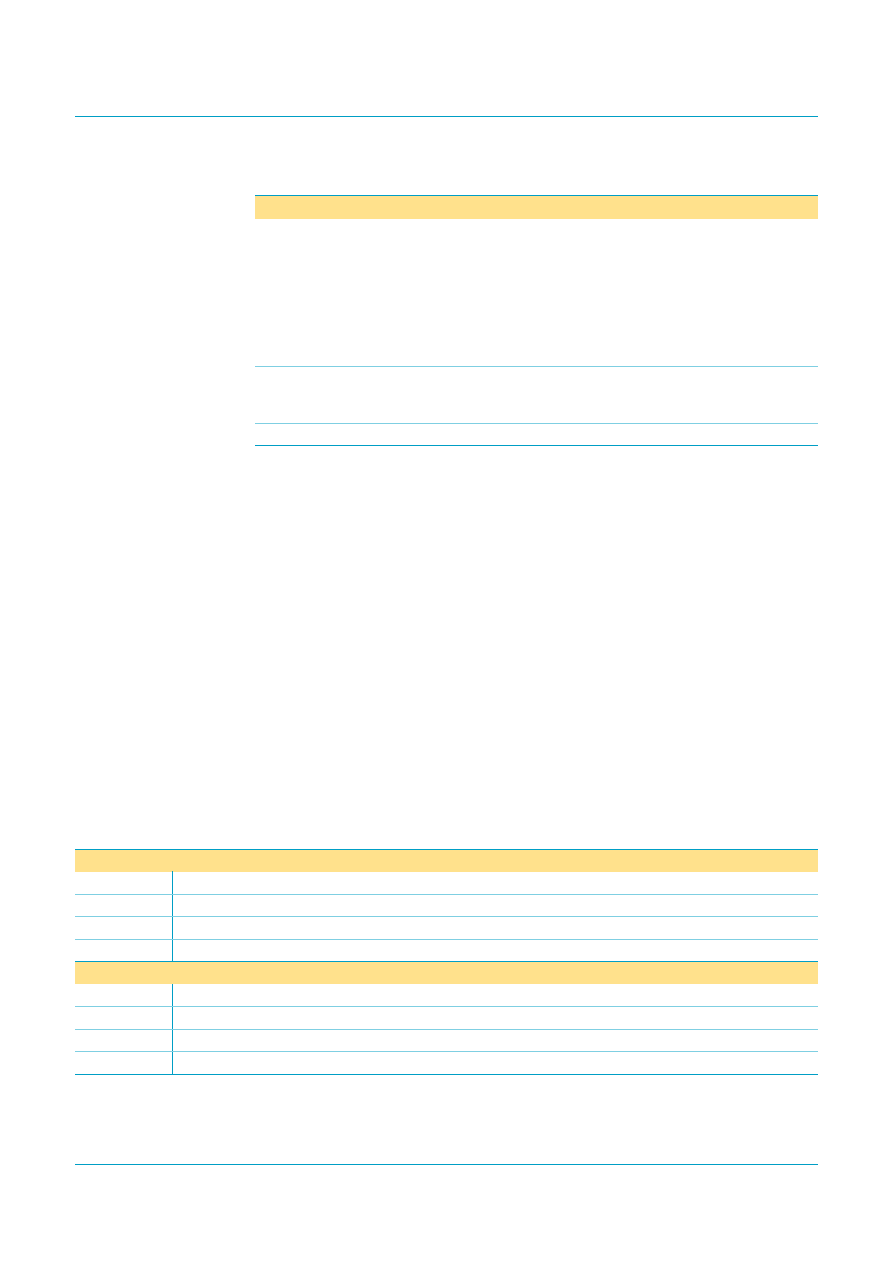

Table 31:

DMA Transfer Counter register: bit allocation

Bit

31

30

29

28

27

26

25

24

Symbol

DMACR4 = DMACR[31:24]

Reset

00H

Bus reset

00H

Access

R/W

Bit

23

22

21

20

19

18

17

16

Symbol

DMACR3 = DMACR[23:16]

Reset

00H

Bus reset

00H

Access

R/W

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 080207R0 | TELEFON-AKKU |

| 080216R0 | TELEFON-AKKU |

| 080219R0 | TELEFON-AKKU |

| 080251R0 | TELEFON-AKKU |

| 935268664112 | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

| 935269987557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-1US1-V1.8 SUBBED TO 935269987557 |

| 935270713557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC CHP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。