- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98071 > S5933QE (APPLIEDMICRO INC) PCI BUS CONTROLLER, PQFP160 PDF資料下載

參數(shù)資料

| 型號: | S5933QE |

| 廠商: | APPLIEDMICRO INC |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PQFP160 |

| 封裝: | PLASTIC, QFP-160 |

| 文件頁數(shù): | 36/176頁 |

| 文件大小: | 823K |

| 代理商: | S5933QE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁當(dāng)前第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁

3-143

PASS-THRU OVERVIEW

S5933

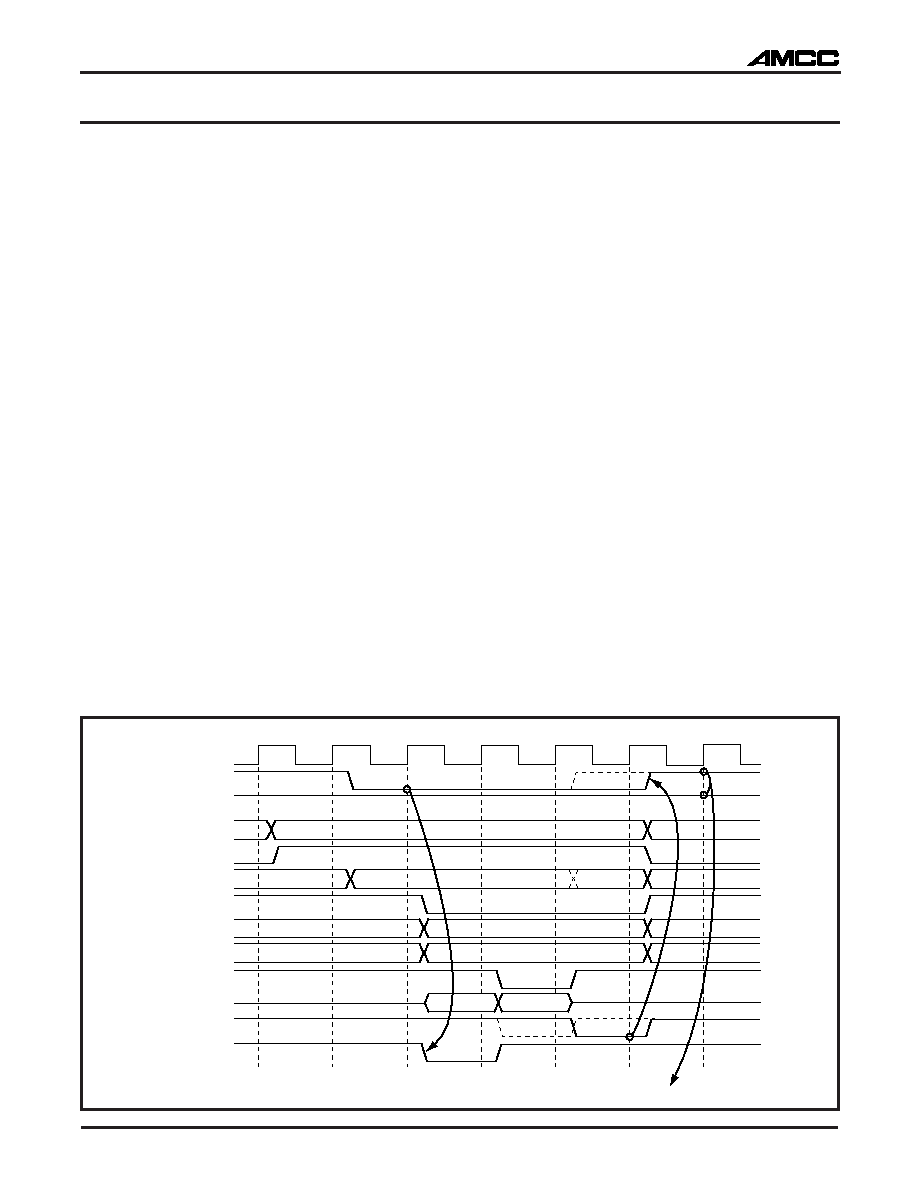

Clock 0: The PCI bus cycle address information is

stored in the S5933 Pass-Thru Address

Register.

Clock 1: The PCI address is recognized as a write

to Pass-Thru region 1. The PCI data is

stored in the S5933 Pass-Thru Data

Register. PTATN# is asserted to indicate a

Pass-Thru access is occurring.

Clock 2: Pass-Thru status signals indicate what

action is required by Add-On logic. Pass-

Thru status outputs are valid when

PTATN# is active and are sampled by the

Add-On at the rising edge of clock 2.

PTBURST#

Deasserted. The access

has a single data phase.

PTNUM[1:0] 01. Indicates the PCI

access is to Pass-Thru

region 1.

PTWR

Asserted. The Pass-Thru

access is a write.

PTBE[3:0]#

0h. Indicates the Pass-Thru

access is 32-bits.

SELECT#, address and byte enable

inputs are driven to read the Pass-Thru

Data Register at offset 2Ch. DQ[31:0] are

driven after RD# and SELECT# are

asserted.

Clock 3: If PTRDY# is asserted at the rising edge

of clock 3, PTATN# is immediately

deasserted and the Pass-Thru access is

completed at clock 4.

Clock 4: If Add-On logic requires more time to read

the Pass-Thru Data Register (slower

memory or peripherals), PTRDY# can be

delayed, extending the cycle. With PTRDY#

asserted at the rising edge of clock 4,

PTATN# is deasserted and the Pass-Thru

access is completed at clock 5.

Clock 5: PTATN# and PTBURST# deasserted at

the rising edge of clock 5 indicates the

Pass-Thru access is complete. The S5933

can accept new Pass-Thru accesses from

the PCI bus at clock 6.

Figure 2 shows a single cycle Pass-Thru write using

the Pass-Thru address information. This provides

PCI cycle address information to select a specific ad-

dress location within an Add-On memory or periph-

eral. Add-On logic must latch the address for use

during the data transfer. Typically, the entire 32-bit

address is not required. The Add-On may implement

a scheme where only the required number of address

bits are latched. It may also be useful to use the

Pass-Thru region identifiers, PTNUM[1:0] as address

lines. For example, Pass-Thru region 1 might be a

64K block of SRAM for data, while Pass-Thru region

2 might be 64K of SRAM for code storage (down-

loaded from the host during initialization). Using

PTNUM0 as address line A16 allows two unique

Add-On memory regions to be defined.

BPCLK

012345

6

0h

1

2Ch

0h

PTATN#

PTBURST#

PTNUM[1:0]

PTWR

PTBE[3:0]#

SELECT#

ADR[6:2]

BE[3:0]#

RD#

DQ[31:0]

PTRDY#

PTADR#

PT ADDR

PT DATA

PCI Write cycle completed

Figure 2. Single Cycle Pass-Thru Write with PTADR#

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| S6A0032 | 16 X 80 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC138 |

| S6A0069 | 16 X 40 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC80 |

| S6A0078 | 34 X 120 DOTS DOT MAT LCD DRVR AND DSPL CTLR, UUC183 |

| S80296SA40 | 16-BIT, 40 MHz, MICROCONTROLLER, PQFP100 |

| S80486-DX4-75-S-V-8-B | 32-BIT, 75 MHz, MICROPROCESSOR, PQFP208 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| S5935 | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S5935_07 | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S59355QRC | 制造商:AppliedMicro 功能描述: |

| S5935QF | 制造商:AMCC 制造商全稱:Applied Micro Circuits Corporation 功能描述:PCI Product |

| S5935QRC | 制造商:AppliedMicro 功能描述:PCI Master Device 160-Pin PQFP |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。