- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369950 > PCI1620PDV Controller Miscellaneous - Datasheet Reference PDF資料下載

參數(shù)資料

| 型號(hào): | PCI1620PDV |

| 英文描述: | Controller Miscellaneous - Datasheet Reference |

| 中文描述: | 控制器雜項(xiàng)-數(shù)據(jù)表參考 |

| 文件頁數(shù): | 62/164頁 |

| 文件大小: | 720K |

| 代理商: | PCI1620PDV |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁當(dāng)前第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁

3

–

20

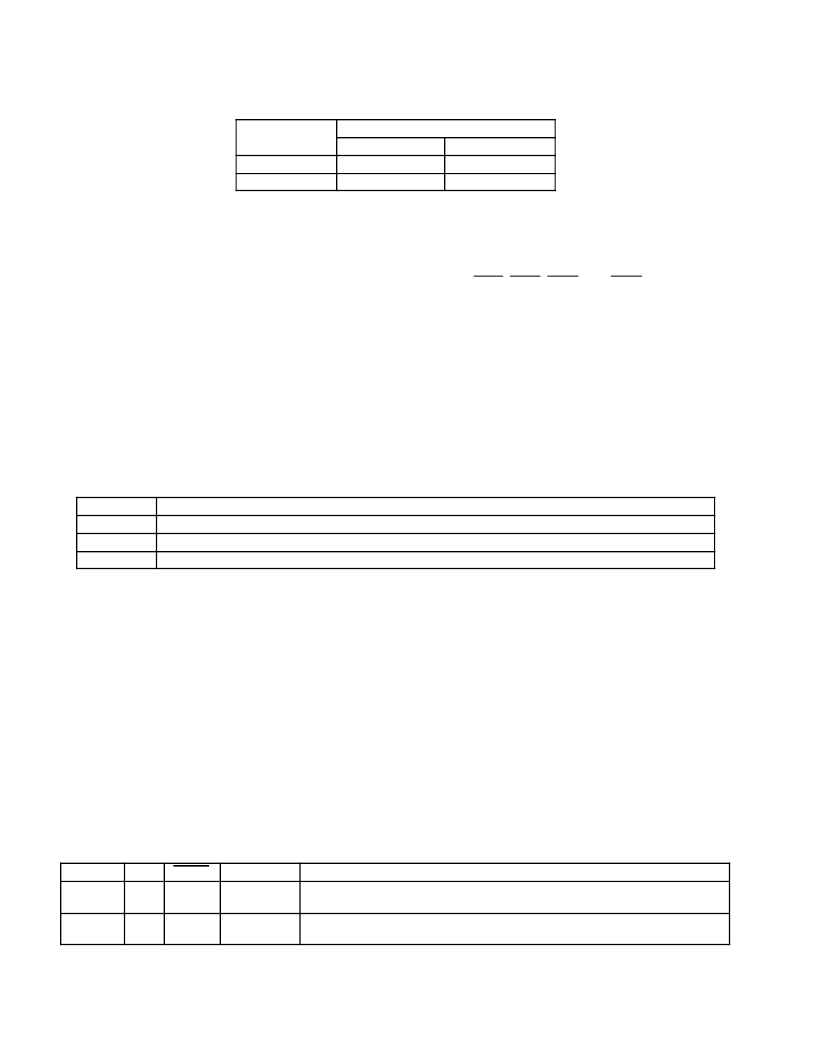

Table 3

–

13. Interrupt Pin Register Cross Reference

INTRTIE BIT

INTPIN

FUNCTION 0

FUNCTION 1

0

01h

02h

1

01h

01h

3.6.5

Using Serialized IRQSER Interrupts

The serialized interrupt protocol implemented in the PCI1620 uses a single terminal to communicate all interrupt

status information to the host controller. The protocol defines a serial packet consisting of a start cycle, multiple

interrupt indication cycles, and a stop cycle. All data in the packet is synchronous with the PCI clock. The packet data

describes 16 parallel ISA IRQ signals and the optional 4 PCI interrupts INTA, INTB, INTC, and INTD. For details on

the IRQSER protocol, refer to the document

Serialized IRQ Support for PCI Systems

.

3.6.6

SMI Support in the PCI1620

The PCI1620 provides a mechanism for interrupting the system when power changes have been made to the PC

Card socket interfaces. The interrupt mechanism is designed to fit into a system maintenance interrupt (SMI) scheme.

SMI interrupts are generated by the PCI1620, when enabled, after a write cycle to either the socket control register

(CB offset 10h, see Section 6.5) of the CardBus register set, or the ExCA power control register (ExCA offset

02h/42h/802h, see Section 5.3) causes a power cycle change sequence to be sent on the power switch interface.

The SMI control is programmed through three bits in the system control register (PCI offset 80h, see Section 4.31).

These bits are SMIROUTE (bit 26), SMISTATUS (bit 25), and SMIENB (bit 24). Table 3

–

14 describes the SMI control

bits function.

Table 3

–

14. SMI Control

BIT NAME

FUNCTION

SMIROUTE

This shared bit controls whether the SMI interrupts are sent as a CSC interrupt or as IRQ2.

SMISTAT

This socket dependent bit is set when an SMI interrupt is pending. This status flag is cleared by writing back a 1.

SMIENB

When set, SMI interrupt generation is enabled. This bit is shared by functions 0 and 1.

If CSC SMI interrupts are selected, then the SMI interrupt is sent as the CSC on a per-socket basis. The CSC interrupt

can be either level or edge mode, depending upon the CSCMODE bit in the ExCA global control register (ExCA offset

1Eh/5Eh/81Eh, see Section 5.20).

If IRQ2 is selected by SMIROUTE, then the IRQSER signaling protocol supports SMI signaling in the IRQ2 IRQ/Data

slot. In a parallel ISA IRQ system, the support for an active low IRQ2 is provided only if IRQ2 is routed to either

MFUNC3 or MFUNC6 through the multifunction routing register (PCI offset 8Ch, see Section 4.38).

3.7

Power Management Overview

In addition to the low-power CMOS technology process used for the PCI1620, various features are designed into the

device to allow implementation of popular power-saving techniques. These features and techniques are discussed

in this section.

3.7.1

Integrated Low-Dropout Voltage Regulator (LDO-VR)

The PCI1620 requires 1.8-V core voltage. The core power can be supplied by the PCI1620 itself using the internal

LDO-VR

. The core power can alternatively be supplied by an external power supply through the VR_OUT terminal.

Table 3

–

15 lists the requirements for both the internal core power supply and the external core power supply.

Table 3

–

15. Requirements for Internal/External 2.5-V Core Power Supply

SUPPLY

VCC

3.3 V

VR_EN

VR_OUT

NOTE

Internal 1.8-V LDO-VR is enabled. A 1.0

μ

F bypass capacitor is required on the VR_PORT

terminal for decoupling. This output is not for external use.

Internal

GND

1.8-V output

External

3.3 V

VCC

1.8-V input

Internal 1.8-V LDO-VR is disabled. An external 1.8-V power supply, of minimum 50-mA

capacity, is required. A 0.1

μ

F bypass capacitor on the VR_OUT terminal is required.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCI2050A | 32-Bit. 66MHz. 9-Master PCI-to-PCI Bridge |

| PCI2050GHK | BUS CONTROLLER |

| PCI2050PDV | BUS CONTROLLER |

| PCI9054AB50BI | Interface IC |

| PCI9036 | Telecommunication IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCI-1620U | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:8-port RS-232 PCI Communication Card, with Surge Protection |

| PCI1620ZHK | 功能描述:外圍驅(qū)動(dòng)器與原件 - PCI PC Card Flash & Smart Card Cntrlr RoHS:否 制造商:PLX Technology 工作電源電壓: 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FCBGA-1156 封裝:Tray |

| PCI-1622A-BE | 制造商:Advantech Co Ltd 功能描述:8PORT RS-422/485 PCI COM CARD - Trays 制造商:Advantech Co Ltd 功能描述:8-port RS-422/485 UPCI COMM card |

| PCI-1622CU | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:8-port RS-422/485 Universal PCI Communication Card with Isolation & EFT Protection |

| PCI-1625U | 制造商:ADVANTECH 制造商全稱:Advantech Co., Ltd. 功能描述:8-port Intelligent RS-232 Universal PCI Communication Card |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。