- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383304 > M5M4V4S40CTP-12 (Mitsubishi Electric Corporation) 4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM PDF資料下載

參數(shù)資料

| 型號: | M5M4V4S40CTP-12 |

| 廠商: | Mitsubishi Electric Corporation |

| 英文描述: | 4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| 中文描述: | 4分(2 -銀行甲131072字x 16位)同步DRAM |

| 文件頁數(shù): | 30/45頁 |

| 文件大小: | 1458K |

| 代理商: | M5M4V4S40CTP-12 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

30

M5M4V4S40CTP-12, -15

Feb ‘97

Preliminary

MITSUBISHI LSIs

4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM

MITSUBISHI ELECTRIC

SDRAM (Rev. 0.3)

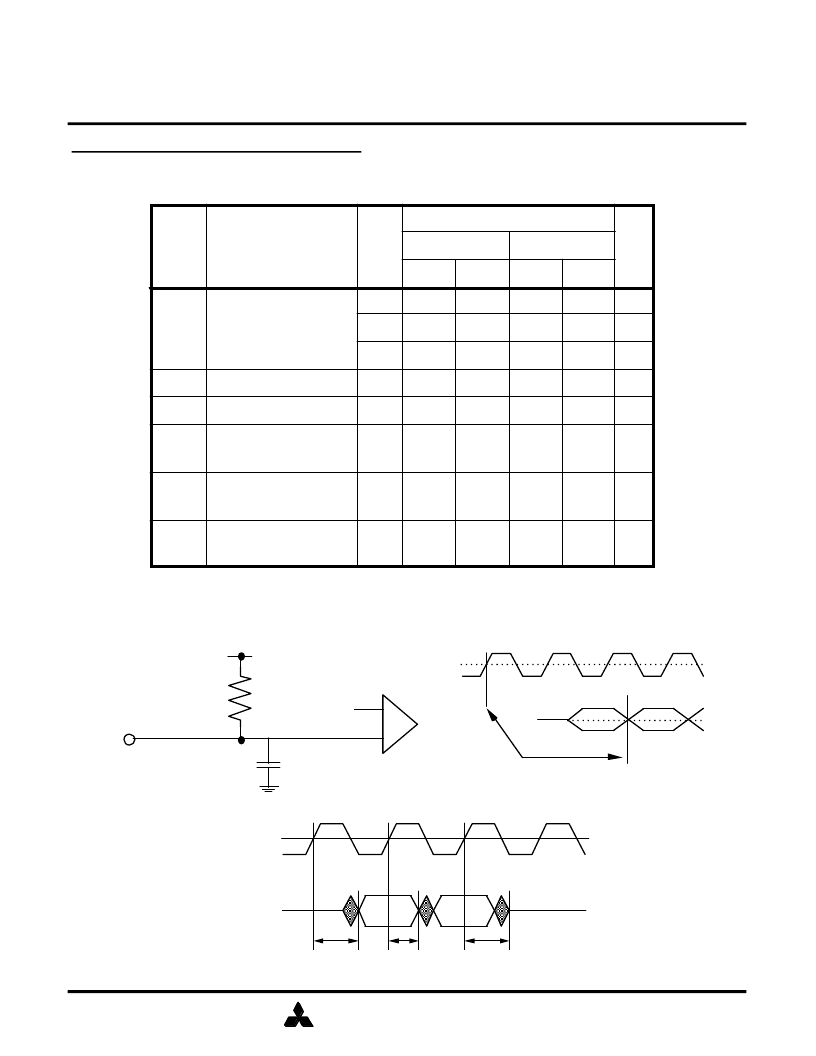

SWITCHING CHARACTERISTICS

(Ta=0 ~ 70°C, Vdd = VddQ = 3.3 ± 0.3v, Vss = VssQ = 0v, unless otherwise noted)

Output Load Condition

Symbol Parameter

Limits

Unit

-12

-15

Min.

Max.

Min.

Max.

tAC

Access time from CLK

CL=1

27

30

ns

CL=2

9.5

12

ns

CL=3

8

9

ns

tCAC

Column Access Time

24.5

30

ns

tRAC

Row Access Time

54.5

60

ns

tOH

Output Hold time from

CLK

3

3

ns

tOLZ

Delay time, output low

impedance from CLK

0

0

ns

tOHZ

Delay time, output high

impedance from CLK

3

8

3

10

ns

V

OUT

V

REF

=1.4V

50pF

50 ohm

V

TT

=1.4V

DQ

CLK

Output Timing Measurement

Reference Point

1.4V

1.4V

1.4V

1.4V

DQ

CLK

tAC

tOH

tOHZ

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M5M4V4S40CTP-15 | 4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S30ATP-10L | 64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-10 | Octal D-Type Transparent Latches With 3-State Outputs 20-TSSOP -40 to 85 |

| M5M4V64S30ATP-12 | 64M (4-BANK x 2097152-WORD x 8-BIT) Synchronous DRAM |

| M5M4V64S30ATP-8 | 30V N-Channel PowerTrench MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M5M4V4S40CTP-15 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:4M (2-BANK x 131072-WORD x 16-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-10L | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-12 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

| M5M4V64S20ATP-8 | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:64M (4-BANK x 4194304-WORD x 4-BIT) Synchronous DRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。