- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄360999 > ISP1583 (NXP Semiconductors N.V.) Hi-Speed Universal Serial Bus peripheral controller PDF資料下載

參數(shù)資料

| 型號(hào): | ISP1583 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Hi-Speed Universal Serial Bus peripheral controller |

| 中文描述: | 高速通用串行總線外設(shè)控制器 |

| 文件頁(yè)數(shù): | 42/87頁(yè) |

| 文件大小: | 420K |

| 代理商: | ISP1583 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)當(dāng)前第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)

Philips Semiconductors

ISP1583

Hi-Speed USB peripheral controller

Product data

Rev. 03 — 12 July 2004

42 of 87

9397 750 13461

Koninklijke Philips Electronics N.V. 2004. All rights reserved.

Each programmable FIFO can be independently configured via its Endpoint

MaxPacketSize register (R/W: 04h), but the total physical size of all enabled

endpoints (IN plus OUT) must not exceed 8192 bytes.

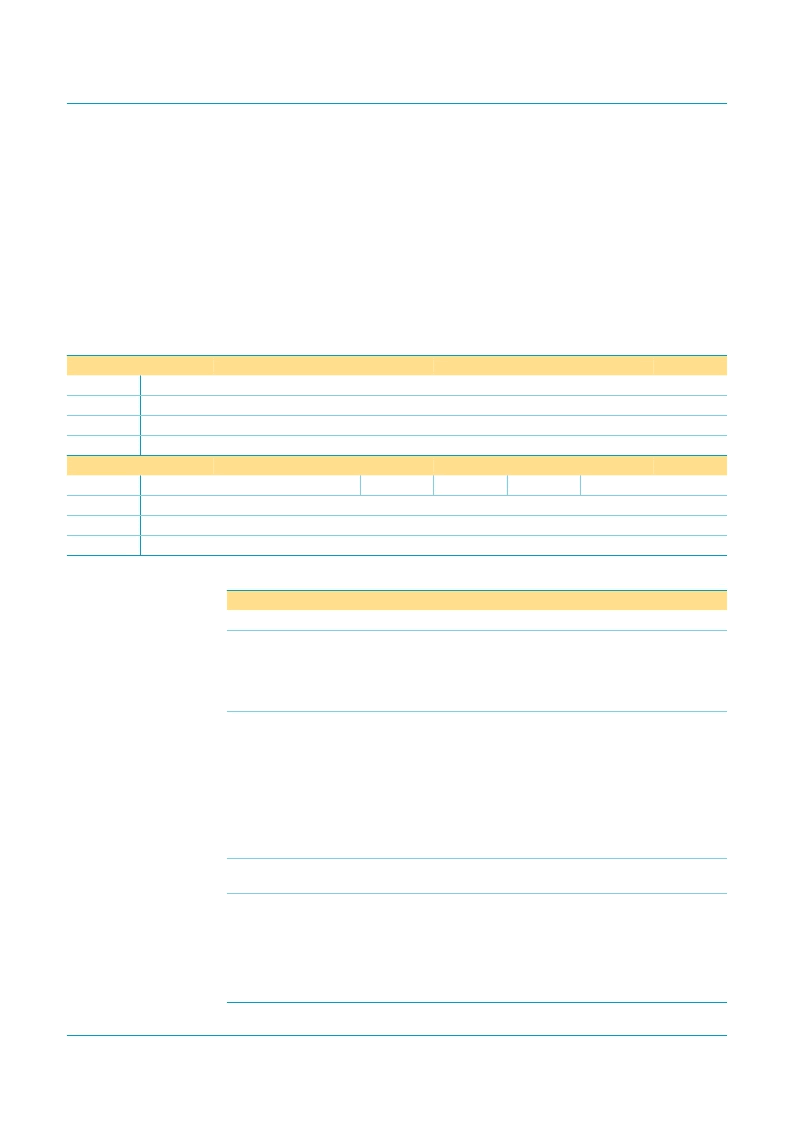

9.3.7

Endpoint Type register (address: 08h)

This register sets the endpoint type of the indexed endpoint: isochronous, bulk or

interrupt. It also serves to enable the endpoint and configure it for double buffering.

Automatic generation of an empty packet for a zero-length TX buffer can be disabled

using bit NOEMPKT. The register contains 2 bytes, and the bit allocation is shown in

Table 45

.

Table 45:

Bit

Symbol

Reset

Bus reset

Access

Bit

Symbol

Reset

Bus reset

Access

Endpoint Type register: bit allocation

15

14

13

12

11

10

9

8

reserved

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

R/W

7

R/W

6

R/W

5

R/W

4

R/W

3

R/W

2

R/W

1

ENDPTYP[1:0]

0

0

R/W

R/W

0

reserved

-

-

R/W

NOEMPKT

0

0

R/W

ENABLE

0

0

R/W

DBLBUF

0

0

R/W

-

-

-

-

0

0

R/W

R/W

R/W

Table 46:

Bit

15 to 5

4

Endpoint Type register: bit description

Symbol

Description

-

reserved

NOEMPKT

No Empty Packet:

Logic 0 causes the ISP1583 to return a null

length packet for the IN token after the DMA IN transfer is

complete. For ATA mode or the DMA IN transfer, which does not

require a null length packet after DMA completion, set to logic 1 to

disable the generation of the null length packet.

ENABLE

Endpoint Enable

: Logic 1 enables the FIFO of the indexed

endpoint. The memory size is allocated as specified in the

Endpoint MaxPacketSize register. Logic 0 disables the FIFO.

Remark:

‘Stall’ing a data endpoint will confuse the Data Toggle bit

on the stalled endpoint because the internal logic picks up from

where it has stalled. Therefore, the Data Toggle bit must be reset

by disabling and re-enabling the corresponding endpoint (by

setting bit ENABLE to logic 0 or logic 1 in the Endpoint Type

register) to reset the PID.

DBLBUF

Double Buffering:

Logic 1 enables double buffering for the

indexed endpoint. Logic 0 disables double buffering.

ENDPTYP[1:0]

Endpoint Type:

These bits select the endpoint type.

3

2

1 to 0

00 —

not used

01 —

Isochronous

10 —

Bulk

11 —

Interrupt.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISP1583BS | Hi-Speed Universal Serial Bus peripheral controller |

| ISP1760BE | Hi-Speed Universal Serial Bus host controller for embedded applications |

| ISP1760 | Hi-Speed Universal Serial Bus host controller for embedded applications |

| ISP1761 | Hi-Speed Universal Serial Bus On-The-Go controller |

| ISP1761BE | Hi-Speed Universal Serial Bus On-The-Go controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISP1583BS | 功能描述:IC USB CTRL HI-SPEED 64HVQFN RoHS:是 類(lèi)別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類(lèi)型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類(lèi)型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱(chēng):Q6396337A |

| ISP1583BS,518 | 功能描述:USB 接口集成電路 USB PERIPH CNTRLR RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1583BS,551 | 功能描述:USB 接口集成電路 HI-SPEED USB2 DEVICE RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1583BS,557 | 功能描述:USB 接口集成電路 DO NOT USE ORDER -S OR -T PART RoHS:否 制造商:Cypress Semiconductor 產(chǎn)品:USB 2.0 數(shù)據(jù)速率: 接口類(lèi)型:SPI 工作電源電壓:3.15 V to 3.45 V 工作電源電流: 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WLCSP-20 |

| ISP1583BS518 | 制造商:ST-Ericsson 功能描述:CONTROLLER USB PERIPHERAL 64HVQFN |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。