- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄370311 > GCIXP1250-232 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | GCIXP1250-232 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁(yè)數(shù): | 62/148頁(yè) |

| 文件大?。?/td> | 1601K |

| 代理商: | GCIXP1250-232 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)當(dāng)前第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)

Intel

IXP1250 Network Processor

62

Datasheet

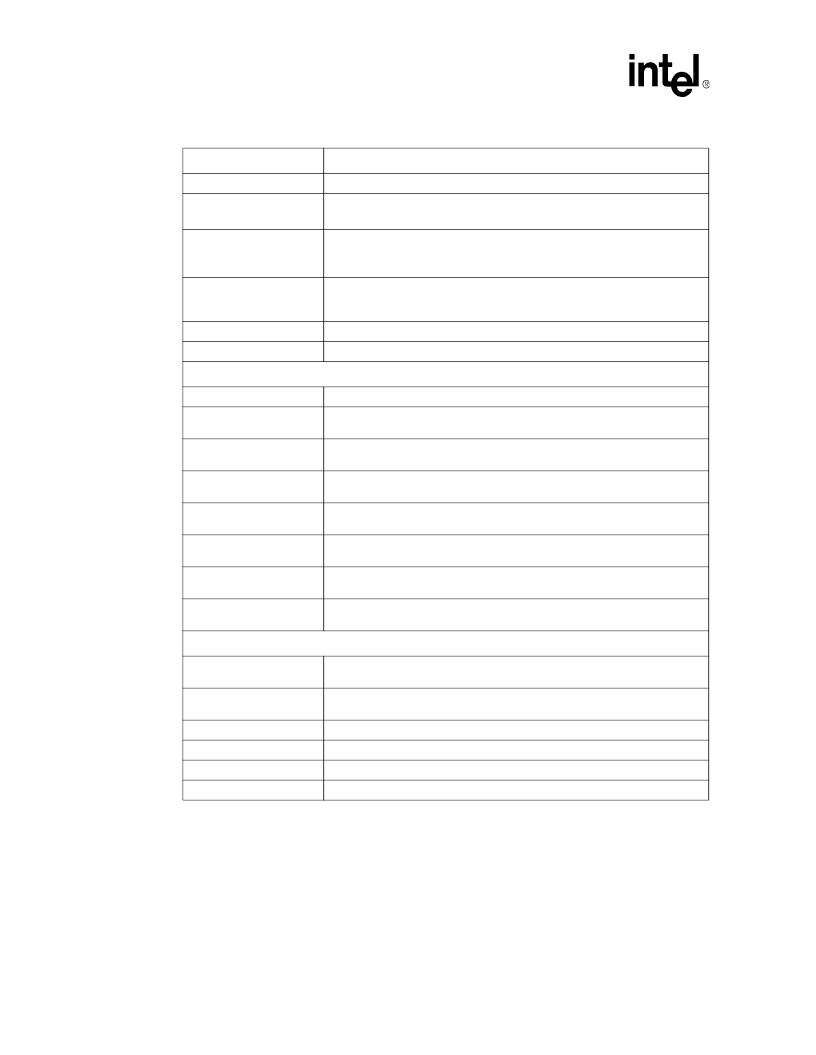

Table 28. 32-bit Unidirectional IX Bus, 3+ MAC Mode

Transmit Path Signals

Description

GPIO[3:1]

Active high outputs, Transmit Port Selects [2:0].

PORTCTL_L[3:2]

Active Low, outputs.

Used with GPIO[0] for transmit device select via external 2-to-4 decoder.

GPIO[0]

Active High, output, transmit enable.

Used with PORTCTL_L[3:2] for transmit device select via external 2-to-4

decoder.

TXAXIS

Active High, output. TXAXIS states are output according to values programmed

in the TFIFO Control field. TXASIS state is output coincident with SOP32 signal,

TXERR state is output coincident with EOP32EOP32 signal.

FBE_L[7:4]

Active Low, output, byte enables for FDAT [63:31].

FDAT[63:31]

Active High, output, 32-bit transmit data.

Receive Path Signals

FPS[2:0]

Active High, output. Receive Port Selects [2:0].

PORTCTL_L[1:0]

Active Low, output. Used with RDYCTL_L[4] for receive device select via

external 2-to-4 decoder.

RDYCTL_L[4]

Active Low, output, receive enable. Used to enable an external 2-to-4 decoder.

Used with PORTCTL_L[1:0].

SOP

Active High, input/output, input receive Start of Packet from the MAC. Driven as

output when bus remains in No-Select state.

EOP

Active High, input/output, input receive End of Packet from the MAC. Driven as

output when bus remains in No-Select state.

RXFAIL

Active Low, input/output, input Receive Error indication from the MAC. Driven as

output when bus remains in No-Select state.

FBE_L[3:0]

Active High, input/output, input byte enables for FDAT [31:0] from the MAC.

Driven as output when bus remains in No-Select state.

FDAT[31:0]

Active High, input/output, input 32-bit receive data from the MAC. Driven as

output when bus remains in No-Select state.

Control Signals Common to both Transmit/Receive Paths

RDYCTL_L[3:0]

Output, 4 bits encoded for Transmit/Receive Ready flags, flow-control, and

inter-chip communication. Decode with external 4-to-16 decoder.

RDYBUS[7:0]

Active High, input/output, Transmit or Receive Ready flags, and flow control

mask data.

TK_IN

Input, not used, must be pulled High in this mode.

TK_OUT

Output, not used, no connect.

FAST_RX1

Active High, ready input from Fast Port 0, pulldown 10 KOhms if not used.

FAST_RX2

Active High, ready input from Fast Port 1, pulldown 10 KOhms if not used.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCK101 | Analog IC |

| GCK131 | Microcontroller |

| GCM-3.15A | Fuse |

| GCM-4A | Fuse |

| GCM-5A | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GCIXP1250BA | 功能描述:IC MPU NETWORK 166MHZ 520-BGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類(lèi)型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類(lèi)型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤(pán) |

| GCIXP1250BB | 功能描述:IC MPU NETWORK 200MHZ 520-BGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類(lèi)型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類(lèi)型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤(pán) |

| GCIXP1250BC | 功能描述:IC MPU NETWORK 232MHZ 520-BGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類(lèi)型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類(lèi)型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤(pán) 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤(pán) |

| GCJ0335C5C0JR50D | 制造商:MURATA 制造商全稱(chēng):Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

| GCJ0335C5C1AR50D | 制造商:MURATA 制造商全稱(chēng):Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。