- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GCIXP1250-232 Microprocessor PDF資料下載

參數(shù)資料

| 型號: | GCIXP1250-232 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 39/148頁 |

| 文件大?。?/td> | 1601K |

| 代理商: | GCIXP1250-232 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁

Intel

IXP1250 Network Processor

Datasheet

39

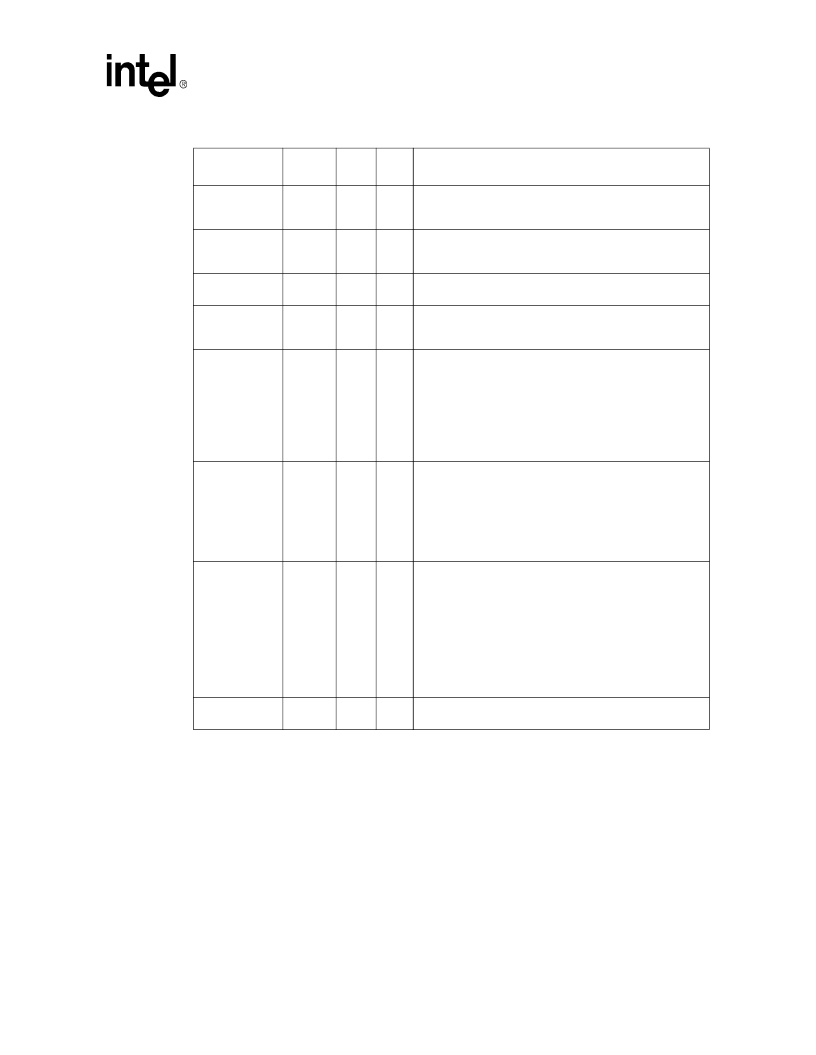

STOP_L

C13

I2/O2/

STS

1

Stop. Indicates that the target is requesting the master to

stop the current transaction. The IXP1250 drives as target

and receives as master.

DEVSEL_L

B13

I2/O2/

STS

1

Device Select. Indicates that the target has decoded its

address as the target of the current access. The IXP1250

drives as target and receives as initiator.

IDSEL

C17

I2

1

Initialization Device Select. Used as Chip Select during PCI

Configuration Space read and write transactions.

PERR_L

D13

I2/O2/

STS

1

Parity error. Used to report data parity errors. The IXP1250

asserts this when it receives bad data parity as target of a

write or master of a read.

SERR_L

E13

I2/O2/

OD

1

System Error.

As an input, it can cause an interrupt to the StrongARM* core

if the IXP1250 is selected for PCI Central Function and

arbitration support (PCI_CFN[1:0]=11).

As an output it can be asserted by the IXP1250 by writing the

SERR bit in the PCI control register, or in response to a PCI

address parity error when not providing PCI Central Function

and arbitration support (PCI_CFN[1:0]=00).

PCI_IRQ_L

B21

I2/O2/

OD

1

PCI Interrupt Request.

As output, used to interrupt the PCI Host Processor. It is

asserted when there is a doorbell set or there are messages

on the I

O outbound post list. This is usually connected to

INTA_L on the PCI Bus.

As Input, It is asserted when there is a doorbell set or there

are messages on the I 2 O outbound post list.

PCI_RST_L

E20

I2/O2/

TS

1

PCI Reset.

When providing PCI Central Function and arbitration

support (PCI_CFN[1:0]=11), PCI _RST_L is an output

controlled by the StrongARM* core. Used to reset the

PCI Bus.

When not providing PCI Central Function and arbitration

(PCI_CFN[1:0]=00), PCI_RST_L is an input, and when

asserted resets the IXP1250 StrongARM* core, all

registers, all transaction queues, and all PCI related

state.

PCI_CLK

D20

I2

1

PCI Clock input. Reference for PCI signals and internal

operations. PCI clock is typically 33 to 66 MHz.

Table 18. PCI Interface Pins (Continued)

PCI Interface

Signal Names

Pin

Number

Type

Total

Pin Descriptions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCK101 | Analog IC |

| GCK131 | Microcontroller |

| GCM-3.15A | Fuse |

| GCM-4A | Fuse |

| GCM-5A | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GCIXP1250BA | 功能描述:IC MPU NETWORK 166MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BB | 功能描述:IC MPU NETWORK 200MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BC | 功能描述:IC MPU NETWORK 232MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCJ0335C5C0JR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

| GCJ0335C5C1AR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。