- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370311 > GCIXP1250-232 Microprocessor PDF資料下載

參數(shù)資料

| 型號(hào): | GCIXP1250-232 |

| 英文描述: | Microprocessor |

| 中文描述: | 微處理器 |

| 文件頁數(shù): | 19/148頁 |

| 文件大?。?/td> | 1601K |

| 代理商: | GCIXP1250-232 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁

Intel

IXP1250 Network Processor

Datasheet

19

BootROM devices may be either 32 bits or 16 bits in width. This is determined by GPIO[3] during

reset. When 16-bit BootROM devices are used, the maximum BootROM address space is reduced

from 8 Mbytes to 4 Mbytes.

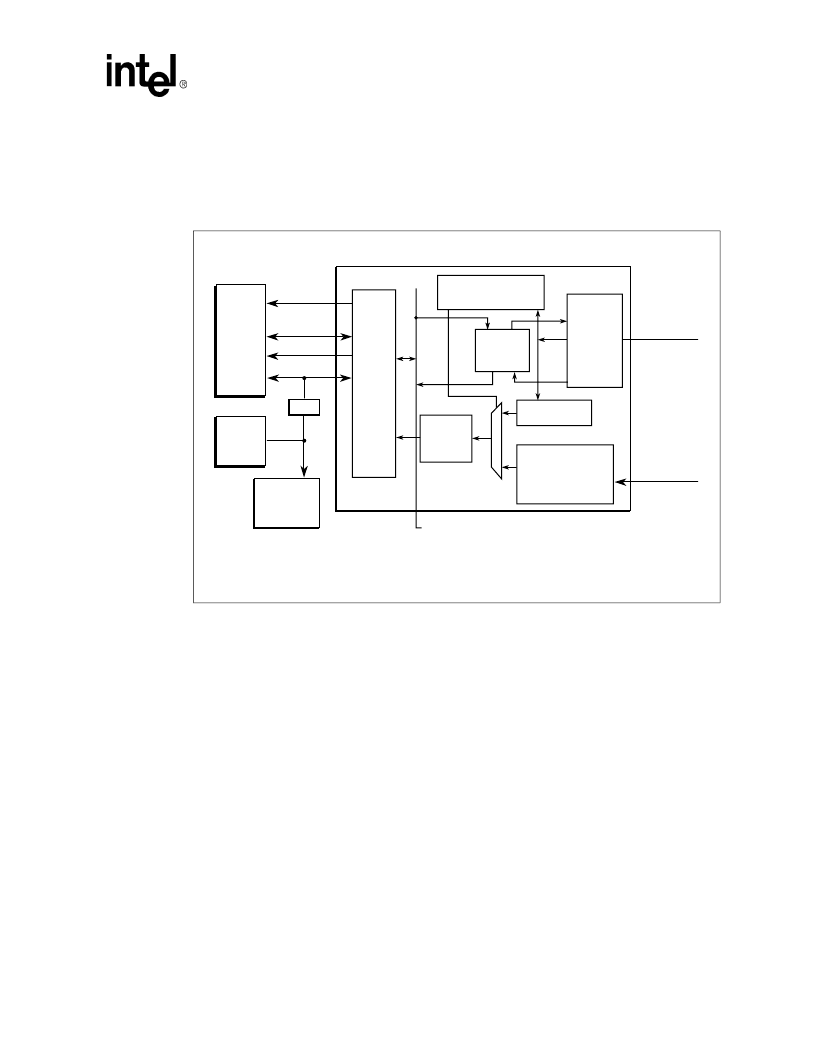

Figure 4

details the major components of the SRAM Unit.

The SRAM Bus consists of 19 address bits, 32 data bits, 4 chip enable bits, 8 buffer and read/write

control signals, a synchronous output clock (SCLK) running at one-half the IXP1250 Core

frequency, and a synchronous input clock (NA/SACLK). When using Flowthru SRAM types, it is

recommended to route the SCLK signal from the SRAMs back to the NA/SACLK input. Routing

this trace identically to the DQ data signals will skew the NA/SACLK slightly to track the return

data trace propagation delay. When using Pipelined/DCD SRAMs, the NA/SACLK input is not

used and may be held inactive with a pulldown to GND to save power.

The SRAM Unit receives memory requests from seven sources: the StrongARM* core and each of

the six Microengines. Refer to the IXP1250 Hardware Reference Manual for details on the

prioritization and queues provided for servicing these requests.

The IXP1250 supports the use of an optional asynchronous ready input for flexibility in interfacing

memory-mapped I/O devices to the SRAM Slowport region. This will allow the I/O device to add

wait-states to IXP1250 I/O accesses. This function is supported on the HIGH_EN_L pin. An I/O

device must drive HIGH_EN_L with a wired-OR open drain buffer configuration, and only drive

the pin when the I/O device is selected.

To use the RDY_L pin function, it must be enabled by setting SRAM_CSR[19]=1. The RDY_L

Pause State Value field located in register SRAM_SLOW_CONFIG[23:16] must be programmed

with the state value at which you choose to pause the internal wait-state logic. This pause state

relates to the other timing parameters programmed into the SRAM_SLOW_CONFIG and

Figure 4. SRAM Unit Block Diagram

A8545-01

AMBA[31:0]

(from

StrongARM*

Core)

Microengine

Commands &

Addresses

Microengine Data [63:0]

SRAM

32KB to

8MB

Pipelined-

DCD or

Flowthru

Buffer

SRAM

Pin

Interface

Command

Decoder

& Address

Generator

Service Priority

(Arbitration)

Machine & Registers

AMBA Bus

Interface

Logic

AMBA Address

Rd/Wr Queue

Microengine Address

& Command Queues

(High Priority, Read,

Readlock Fail

and Order)

Memory/

AMBA Data

FIFO

Addr[18:0]

Data[31:0]

RD/WR/EN

Signals

addr

data

* Other names and brands may be claimed as the property of others.

** ARM architecture compatible

BootROM

256KB

to

8 MB

Peripheral

Device

(i.e., MAC

CPU port)

SCLK

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GCK101 | Analog IC |

| GCK131 | Microcontroller |

| GCM-3.15A | Fuse |

| GCM-4A | Fuse |

| GCM-5A | Fuse |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GCIXP1250BA | 功能描述:IC MPU NETWORK 166MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BB | 功能描述:IC MPU NETWORK 200MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCIXP1250BC | 功能描述:IC MPU NETWORK 232MHZ 520-BGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

| GCJ0335C5C0JR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

| GCJ0335C5C1AR50D | 制造商:MURATA 制造商全稱:Murata Manufacturing Co., Ltd. 功能描述:Chip Monolithic Ceramic Capacitors |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。