- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369517 > BT849A Single-Chip Video Capture for PCI PDF資料下載

參數(shù)資料

| 型號(hào): | BT849A |

| 英文描述: | Single-Chip Video Capture for PCI |

| 中文描述: | 單芯片的PCI視頻捕捉 |

| 文件頁(yè)數(shù): | 58/141頁(yè) |

| 文件大小: | 1149K |

| 代理商: | BT849A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)當(dāng)前第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)

Bt848/848A/849A

Single-Chip Video Capture for PCI

Brooktree

48

F

UNCTIONAL

D

ESCRIPTION

DMA Controller

L848A_A

Target Memory

The Bt848’s FIFO DWORDs are perfectly aligned to the PCI bus, i.e. bit 0 of the

FIFO DWORDs lines up with bit AD[0] on the PCI bus. Thus, video scan line data

is aligned to target memory locations, and data path combinational logic between

the FIFO and the PCI bus is not required.

The target memory for a given scan line of data is assumed to be linear, incre-

menting, and contiguous. For a 1024-pixel scan line a maximum of 4 KB of con-

tiguous physical memory is required. Each scan line can be stored anywhere in the

32-bit address space. A scan line can be broken into segments with each segment

sent to a different target area. An image buffer can be allocated to line fragments

anywhere in the physical memory, as the line sequence is arbitrary.

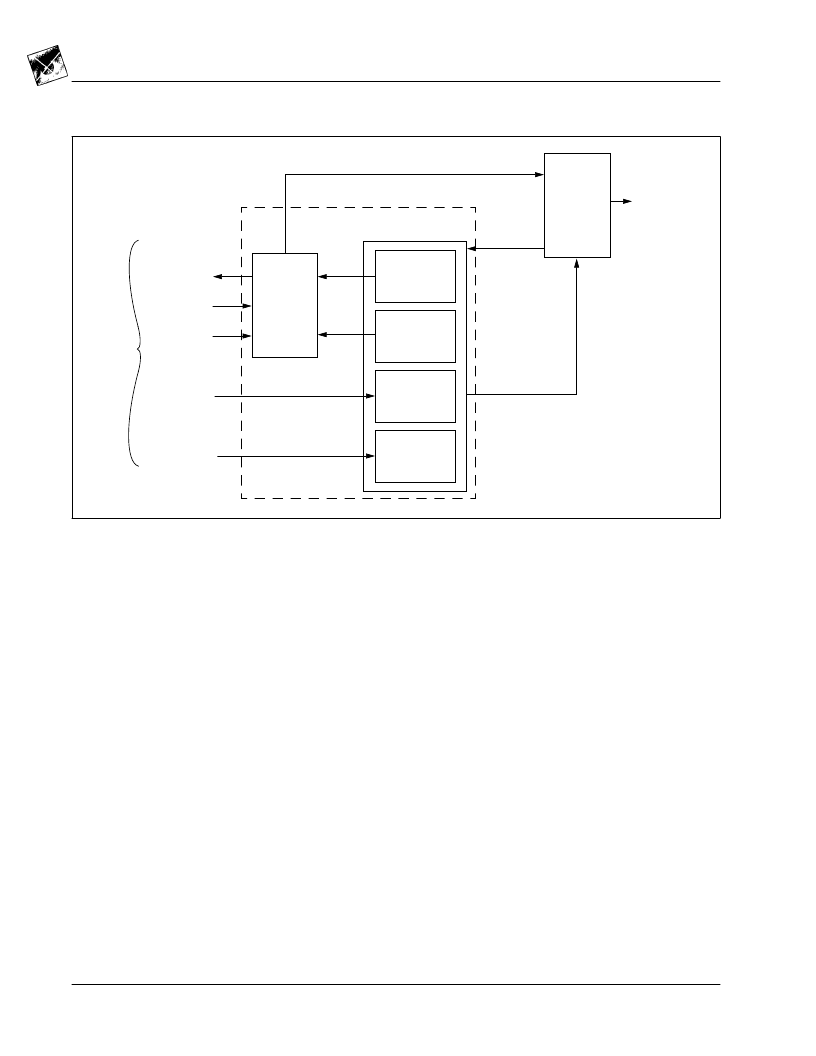

Figure 23. RISC Block Diagram

RISC

Instruction

Buffer

DMA

Address

and

Byte Counter

FIFO Data

Buffer

RISC

Program

Counter

Address/Data

Decoder

RISC

Decoder

PCI

Initiator

Control Signals

Op

Code

To PCI Bus

Interface

Pixel Data [31:0]

Address

RISC

Instructions

FIFO Read

Signals

FIFO Status

Bits

Number of

Bytes

Available

in FIFO

FIFO

Output [31:0]

From

FIFO

DMA Controller

RISC Program

Start Address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BT8510EPJC | PCM Transceiver |

| BT857KPJ | Color Encoder Circuit |

| BT8958EHJ50 | xDSL Interface |

| BT8953AEPFC | xDSL Interface |

| BT8953AEPJ | xDSL Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BT849AKPF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Chip Video Capture for PCI |

| BT850-SA | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-SA-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

| BT850-ST | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-ST-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULEE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。