- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369517 > BT849A Single-Chip Video Capture for PCI PDF資料下載

參數(shù)資料

| 型號: | BT849A |

| 英文描述: | Single-Chip Video Capture for PCI |

| 中文描述: | 單芯片的PCI視頻捕捉 |

| 文件頁數(shù): | 18/141頁 |

| 文件大?。?/td> | 1149K |

| 代理商: | BT849A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁

Bt848/848A/849A

Single-Chip Video Capture for PCI

Brooktree

8

F

UNCTIONAL

D

ESCRIPTION

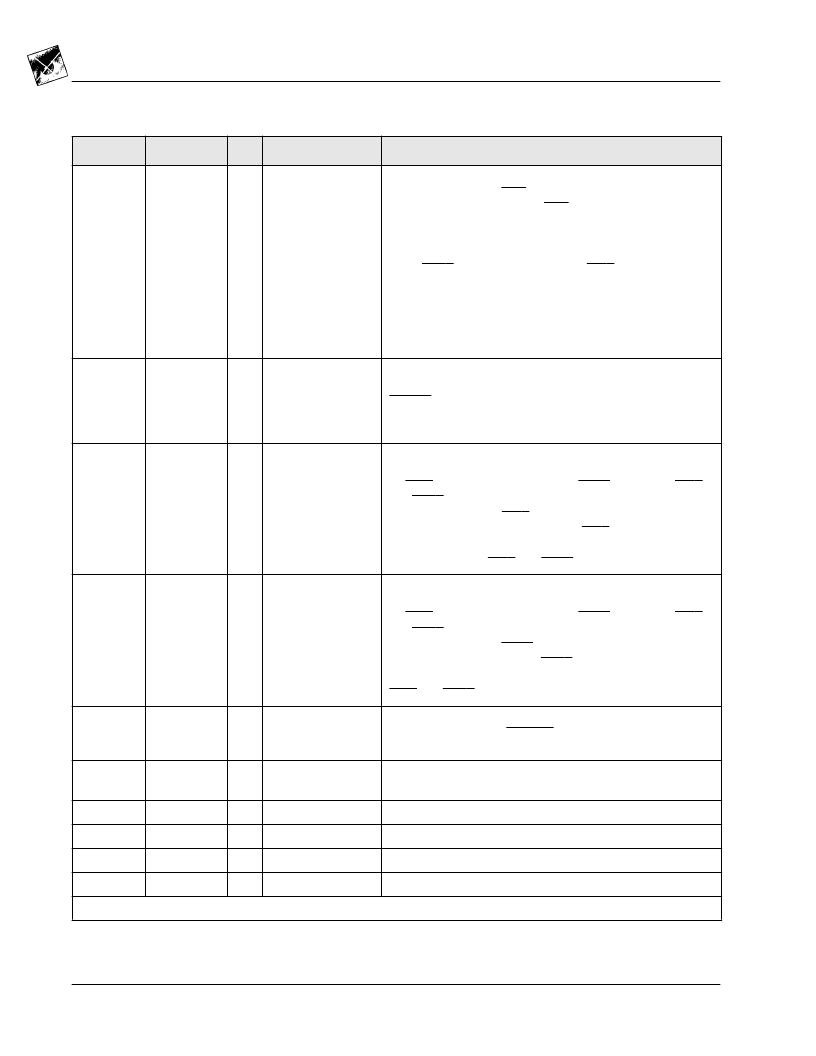

Pin Descriptions

L848A_A

51

PAR

I/O

Parity

This three-state, bi-directional, I/O pin provides even parity

across AD[31:0] and CBE[3:0]. This means that the number

of 1’s on PAR, AD[31:0], and CBE[3:0] equals an even num-

ber.

PAR is stable and valid one clock after the address phase.

For data phases, PAR is stable and valid one clock after

either TRDY is asserted on a read or IRDY is asserted on a

write. Once valid, PAR remains valid until one clock after the

completion of the current data phase. PAR and AD[31:0] have

the same timing, but PAR is delayed by one clock. The target

drives PAR for read data phases; the master drives PAR for

address and write data phases.

42

FRAME

I/O

Cycle Frame

This sustained three-state signal is driven by the current

master to indicate the beginning and duration of an access.

FRAME is asserted to signal the beginning of a bus transac-

tion. Data transfer continues throughout assertion. At deas-

sertion, the transaction is in the final data phase.

43

IRDY

I/O

Initiator Ready

This sustained three-state signal indicates the bus master’s

readiness to complete the current data phase.

IRDY is used in conjunction with TRDY. When both IRDY

and TRDY are asserted, a data phase is completed on that

clock. During a read, IRDY indicates when the initiator is

ready to accept data. During a write, IRDY indicates when the

initiator has placed valid data on AD[31:0]. Wait cycles are

inserted until both IRDY and TRDY are asserted together.

44

TRDY

I/O

Target Ready

This sustained three-state signal indicates the target’s readi-

ness to complete the current data phase.

IRDY is used in conjunction with TRDY. When both IRDY

and TRDY are asserted, a data phase is completed on that

clock. During a read, TRDY indicates when the target is pre-

senting data. During a write, TRDY indicates when the target

is ready to accept the data. Wait cycles are inserted until both

IRDY and TRDY are asserted together.

45

DEVSEL

I/O

Device Select

This sustained three-state signal indicates device selection.

When actively driven, DEVSEL indicates the driving device

has decoded its address as the target of the current access.

46

STOP

I/O

Stop

This sustained three-state signal indicates the target is

requesting the master to stop the current transaction.

49

PERR

I/O

Parity Error

Report data parity error.

14

REQ

O

Request

Agent desires bus.

8

INTA

O

Interrupt A

This signal is an open drain interrupt output.

50

SERR

O

System Error

Report address parity error. Open drain.

See PCI Specification 2.1 for further documentation

Table 2. Pin Descriptions Grouped by Pin Function

(2 of 6)

Pin #

Pin Name

I/O

Signal

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BT8510EPJC | PCM Transceiver |

| BT857KPJ | Color Encoder Circuit |

| BT8958EHJ50 | xDSL Interface |

| BT8953AEPFC | xDSL Interface |

| BT8953AEPJ | xDSL Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BT849AKPF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Chip Video Capture for PCI |

| BT850-SA | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-SA-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

| BT850-ST | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-ST-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULEE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。