- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369517 > BT849A Single-Chip Video Capture for PCI PDF資料下載

參數(shù)資料

| 型號: | BT849A |

| 英文描述: | Single-Chip Video Capture for PCI |

| 中文描述: | 單芯片的PCI視頻捕捉 |

| 文件頁數(shù): | 104/141頁 |

| 文件大小: | 1149K |

| 代理商: | BT849A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁當(dāng)前第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁

Bt848/848A/849A

Single-Chip Video Capture for PCI

Brooktree

94

C

ONTROL

R

EGISTER

D

EFINITIONS

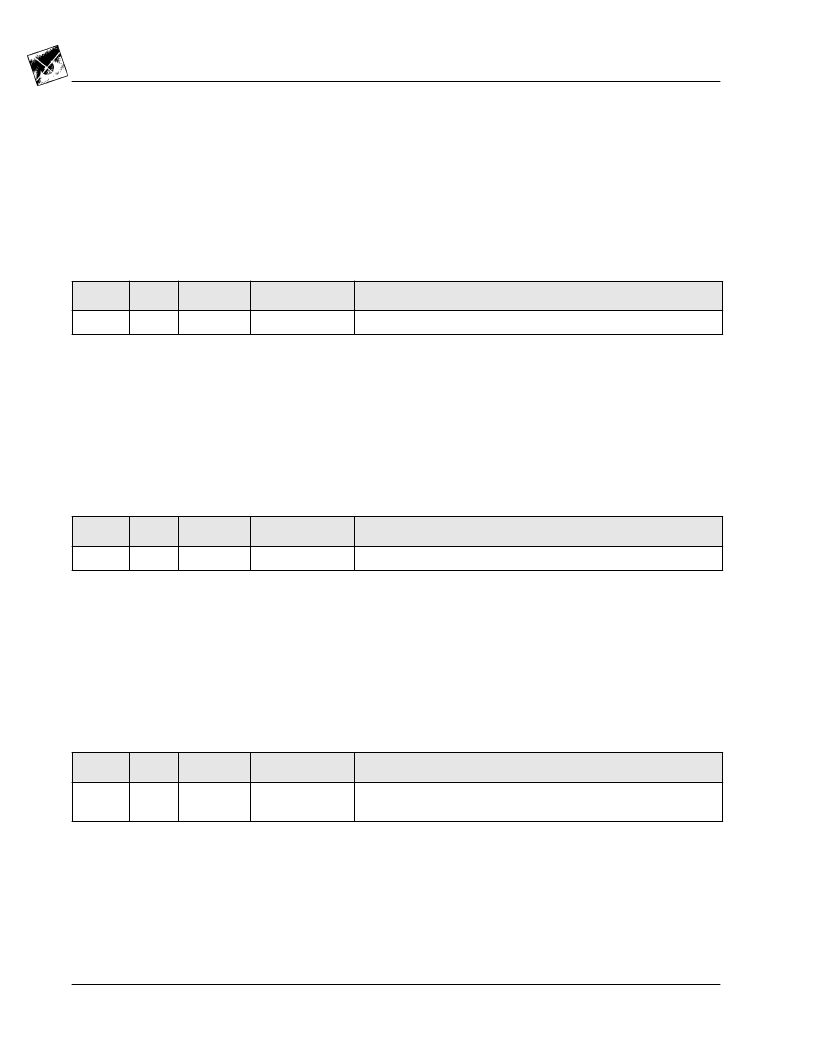

Vertical Delay Register, Lower Byte

L848A_A

Vertical Delay Register, Lower Byte

Memory Mapped Location 0x010 – Even Field (E_VDELAY_LO)

Memory Mapped Location 0x090 – Odd Field (O_VDELAY_LO)

Upon reset it is initialized to 0x16. VDELAY_LO(0) is the least significant bit. This 8-bit register is the lower byte of

the 10-bit VDELAY register. The two MSBs of VDELAY are contained in the CROP register. VDELAY defines the

number of half lines between the trailing edge of VRESET and the start of active video.

Vertical Active Register, Lower Byte

Memory Mapped Location 0x014 – Even Field (E_VACTIVE_LO)

Memory Mapped Location 0x094 – Odd Field (O_VACTIVE_LO)

Upon reset it is initialized to 0xE0. VACTIVE_LO(0) is the least significant bit. This 8-bit register is the lower byte

of the 10-bit VACTIVE register. The two MSBs of VACTIVE are contained in the CROP register. VACTIVE defines

the number of lines used in the vertical scaling process.

Horizontal Delay Register, Lower Byte

Memory Mapped Location 0x018 – Even Field (E_DELAY_LO)

Memory Mapped Location 0x098 – Odd Field (O_DELAY_LO)

Upon reset it is initialized to 0x78. HDELAY_LO(0) is the least significant bit. This 8-bit register is the lower byte

of the 10-bit HDELAY register. The two MSBs of HDELAY are contained in the CROP register. HDELAY defines

the number of scaled pixels between the falling edge of HRESET and the start of active video.

Bits

Type

Default

Name

Description

[7:0]

RW

0x16

VDELAY_LO

The least significant byte of the vertical delay register.

Bits

Type

Default

Name

Description

[7:0]

RW

0xE0

VACTIVE_LO

The least significant byte of the vertical active register.

Bits

Type

Default

Name

Description

[7:0]

RW

0x78

HDELAY_LO

The least significant byte of the horizontal delay register. HACTIVE

pixels will be output by the chip starting at the fall of HRESET.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BT8510EPJC | PCM Transceiver |

| BT857KPJ | Color Encoder Circuit |

| BT8958EHJ50 | xDSL Interface |

| BT8953AEPFC | xDSL Interface |

| BT8953AEPJ | xDSL Interface |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BT849AKPF | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Single-Chip Video Capture for PCI |

| BT850-SA | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-SA-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

| BT850-ST | 功能描述:BTV4.2 DUAL MODE USB HCI MODULE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:1 |

| BT850-ST-T/R | 功能描述:BTV4.2 DUAL MODE USB HCI MODULEE 制造商:laird - wireless & thermal systems 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:2,500 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。