- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385942 > TNETA1560 (Texas Instruments, Inc.) ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) PDF資料下載

參數(shù)資料

| 型號: | TNETA1560 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ATM Segmentation and Reassembly Device with SBUS Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) |

| 中文描述: | 自動(dòng)柜員機(jī)分段和重組與SBus主機(jī)接口(自動(dòng)柜員機(jī)分段和重設(shè)裝置帶SBU的主機(jī)接口設(shè)備) |

| 文件頁數(shù): | 39/40頁 |

| 文件大小: | 804K |

| 代理商: | TNETA1560 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當(dāng)前第39頁第40頁

TNETA1560

ATM SEGMENTATION AND REASSEMBLY DEVICE

WITH SBUS HOST INTERFACE

SDNS010C – JANUARY 1994 – REVISED OCTOBER 1995

39

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

PRINCIPLES OF OPERATION

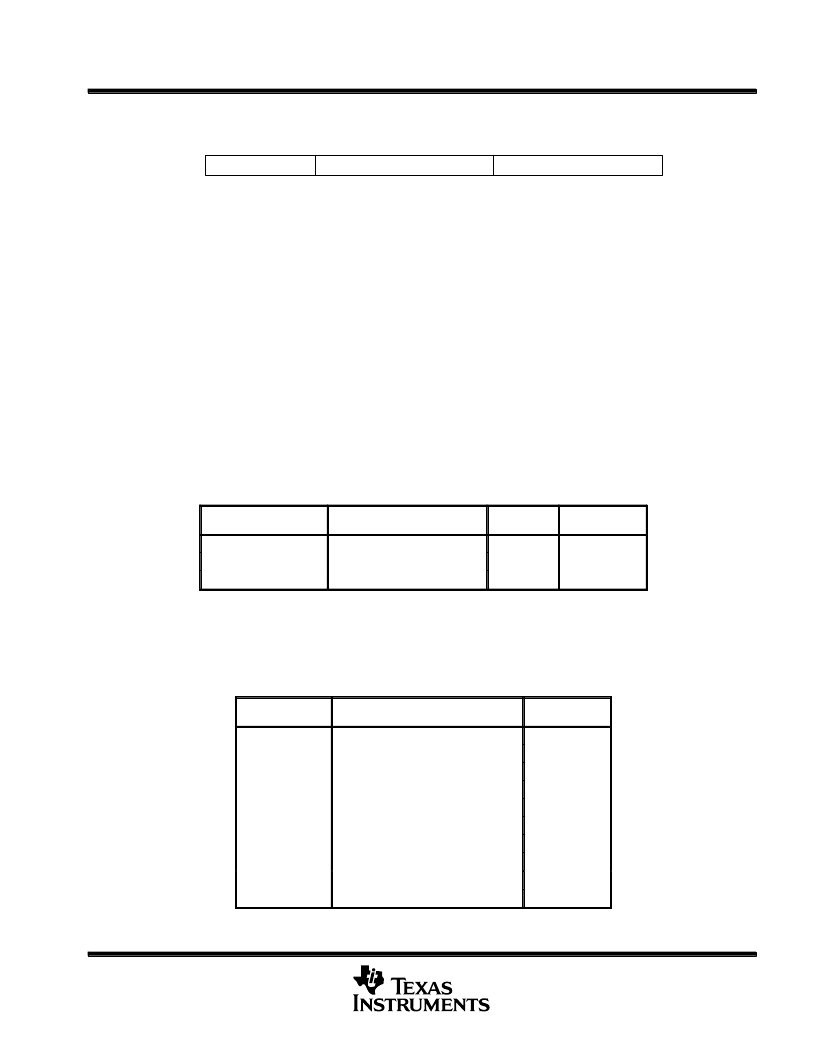

FIFO-maximum-depth registers

Unused (bits 31 – 20) Max_RX_FIFO_Depth (bits 19 – 10)

Max_TX_FIFO_Depth (bits 9 – 0)

This is the only set of statistics collected by the SAR, which is useful information for queuing analysis in different

platforms with varying SBus-clock speeds and latencies. These registers are not of the read-and-reset variety

and must be explicitly set to zero to restart the measurement.

SBus physical-address mapping (in SBus-slave mode)

The SAR allows the host to access various peripheral devices and internal registers via an SBus-slave mode.

The device connects to the SBus physical-address bits (15–0) and (24–23). To access the PHY-layer register,

the software driver uses the SBus address offset given in Table 13. The SBus interface on the TNETA1560 uses

byte addressing to access the PHY-layer registers. During read operations, the data byte received from the

PHY-layer device is copied four times to make a 32-bit data word that is transferred across the bus. In a write

operation to a PHY-layer register, the software writes a valid data byte on SBD31–SBD24 because the SBus

uses the big-endian convention.

The accesses to the EPROM are similar to the read operations to the PHY-layer registers with the difference

being that the SBACK signals are set to 101 to indicate byte accesses.

peripheral devices

Table 13 specifies the SAR-slave mode SBus physical-address ranges for the SAR peripheral devices.

Table 13. SBus Physical Addresses for SAR Peripheral Devices

ADDRESS – 24 BITS

(hex)

000000-00FFFF

DESCRIPTION

ADDRESS

BITS

16

READ/WRITE

EPROM addresses

Read only

400000-40FFFF

PHY-layer register addresses

16

Read/write

C00000-C0FFFF

Control-memory addresses

14

Read/write

SBus SAR registers

The SBus SAR internal registers have an SBus physical-address base value of hex 800000. Table 14 specifies

the offset from this address for various SAR registers.

Table 14. SBus Physical Addresses for SAR Registers

OFFSET – 8 BIT

(hex)

00

DESCRIPTION

READ/WRITE

Software reset

Write only

04

Status register

Read only

08

Interrupt-mask register

Read/write

0C

Configuration register

Read/write

10

Reserved

14

BWG-table-size register

Read/write

18

TX/RX FIFO-maximum-depth register

Read/write

1C

Reserved

20

Clear-transmit-freeze command

Write only

24

Clear-receive-freeze command

Write only

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TNETA1561 | ATM Segmentation and Reassembly Device with PCI Host Interface(ATM 分段和重設(shè)裝置帶SBUS主機(jī)接口) |

| TNETA1600 | SONET/SDH ATM Receiver/Transmitter for 622.08-Mit/s or 155.52-Mbit/s Operation(SONET/SDH ATM接收器/傳送器) |

| TNETA1610 | STS-12c/STM-4 Receiver/Transmitter with Clock Recovery/Generation(STS-12C/STM-4接收/傳送器) |

| TNETA1611 | STS-12c/STM-4 Receiver/Transimitter(STS-12C/STM-4接收/傳送器) |

| TNETA1630 | 622.08-MHz Clock-Recovery Device(622.08-MHz時(shí)鐘發(fā)生裝置) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TNETA1560MFP | 制造商:Rochester Electronics LLC 功能描述: 制造商:Texas Instruments 功能描述: |

| TNETA1560PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1561PGC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TNETA1570 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:ATM SEGMENTATION AND REASSEMBLY DEVICE WITH INTEGRATED 64-BIT PCI-HOST INTERFACE |

| TNETA1570MFP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:ATM/SONET Segmentation and Reassembly Circuit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。