- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄369993 > Pentium III cpu with mobile (Intel Corp.) Pentium III processor Mobile Module Connector 2 (MMC-2)(帶移動模塊連接器2奔III處理器) PDF資料下載

參數(shù)資料

| 型號: | Pentium III cpu with mobile |

| 廠商: | Intel Corp. |

| 英文描述: | Pentium III processor Mobile Module Connector 2 (MMC-2)(帶移動模塊連接器2奔III處理器) |

| 中文描述: | 奔騰III處理器的移動模塊連接器2(絲裂霉素2)(帶移動模塊連接器2奔三處理器) |

| 文件頁數(shù): | 19/64頁 |

| 文件大?。?/td> | 773K |

| 代理商: | PENTIUM III CPU WITH MOBILE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁

Pentium

III Processor Mobile Module MMC-2

245304-003

Datasheet

13

3.1.7

Clock Signals

Table 7

provides descriptions of the clock signals.

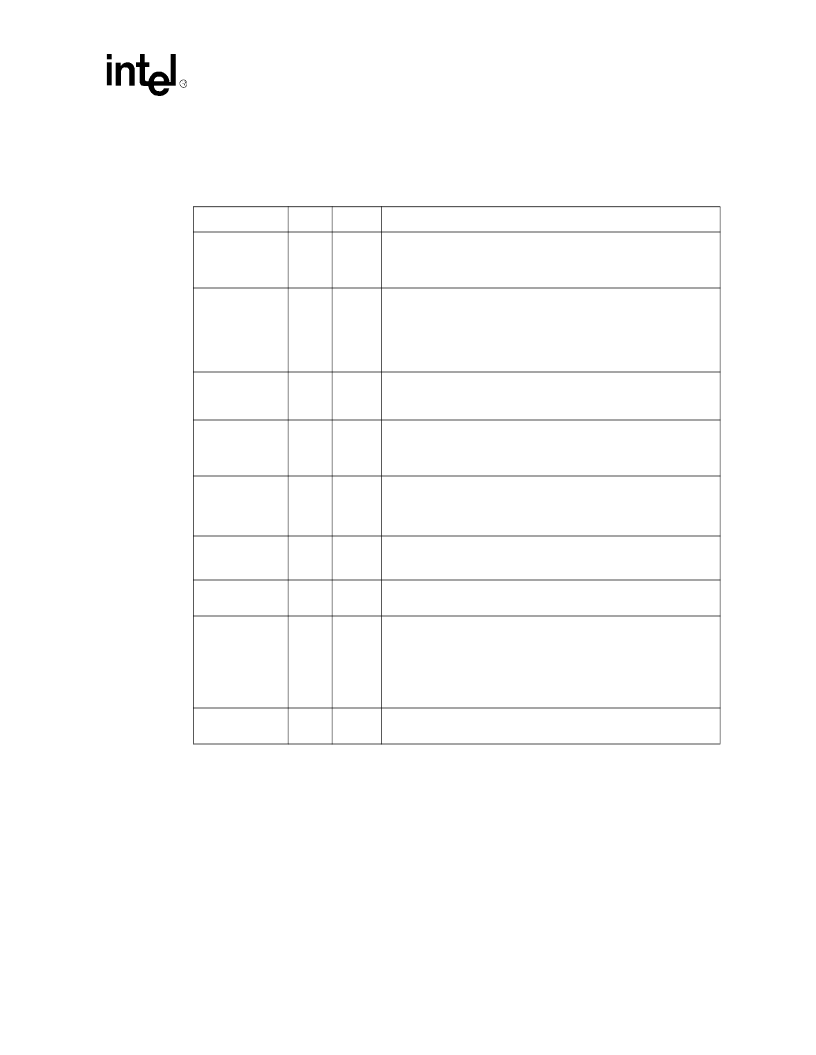

Table 7. Clock Signal Descriptions

Name

Type

Voltage

Description

PCLK

I

PCI

V_3

PCI Clock In:

PCLK, an input to the mobile module, is one of the

system

’

s PCI clocks.

All of the 82443BX Host Bridge logic uses this

clock in the PCI clock domain.

This clock is stopped when the PIIX4E/

M PCI_STP# signal is asserted and/or during all suspend states.

HCLK0

I

CMOS

V_CLK

Host Clock In:

This clock is an input to the mobile module from the

CK100-M/CK100-SM clock source. The processor and the 82443BX

Host Bridge system controller use HCLK0. This clock is stopped when

the PIIX4E/M CPU_STP# signal is asserted and/or during all suspend

states.

Note

: HCLK0 and BCLK are used interchangeably.

HCLK1

I

CMOS

V_CLK

Host Clock In:

This clock is an input to the mobile module from the

CK100-M/CK100-SM clock source.

This signal is not implemented on the mobile module.

DCLK0

O

CMOS

V_3

SDRAM Clock Out:

A 66-MHz SDRAM clock reference generated

internally by the 82443BX Host Bridge system controller onboard PLL.

It feeds an external buffer that produces multiple copies for the SO-

DIMMs.

DCLKRD

I

CMOS

V_3

SDRAM Read Clock:

Feedback reference from the SDRAM clock

buffer. The 82443BX Host Bridge System Controller uses this clock

when reading data from the SDRAM array.

This signal is not implemented on the mobile module.

DCLKWR

I

CMOS

V_3

SDRAM Write Clock:

Feedback reference from the SDRAM clock

buffer. The 82443BX Host Bridge system controller uses this clock

when writing data to the SDRAM array.

GCLKIN

I

CMOS

V_3

AGP Clock In:

The GCLKIN input is a feedback reference from the

GCLKO signal.

GCLKO

O

CMOS

V_3

AGP Clock Out:

This signal is generated by the 82443BX Host

Bridge system controller onboard PLL from the HCLK0 host clock

reference. The frequency of GCLKO is 66 MHz. The GCLKO output is

used to feed both the PLL reference input pins on the 82443BX Host

Bridge system controller and the AGP device. The board layout must

maintain complete symmetry on loading and trace geometry to

minimize AGP clock skew.

FQS

O

CMOS

V_3S

Frequency Select:

This output indicates the desired host clock

frequency for the mobile module.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| pentium III CPU | Pentium III Processor for the SC242 at 450MHz to 1.0GHz(SC242工作頻率450MHZ到1GHZ奔III處理器) |

| pentium III processor | 32 bit Processor Mobile Module(32 位帶移動模塊處理器) |

| Pentium OverDrive Processor | Pentium OverDrive Processor With MMX Technology For Pentium Processor-Based System(帶MMX技術(shù)奔騰超速轉(zhuǎn)動處理器) |

| pentium pro processor | Pentium Pro Processor with 1MB L2 Cache at 200MHZ(1兆比特L2高速緩存頻率200兆赫茲處理器) |

| pentium processor with MMX | 32-bit processor with MMX technology(32位帶MMX技術(shù)處理器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| P-ENV568K3G3 | 制造商:Panasonic Industrial Company 功能描述:TUNER |

| PEO14012 | 制造商:TE Connectivity 功能描述:RELAY SPCO 12VDC |

| PEO14024 | 制造商:TE Connectivity 功能描述:RELAY SPCO 24VDC |

| PEO96742 | 制造商:Delphi Corporation 功能描述:ASM TERM |

| PEOODO3A | 制造商:MACOM 制造商全稱:Tyco Electronics 功能描述:Versatile Power Entry Module with Small Footprint |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。