- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45388 > MSC8102M4000 (MOTOROLA INC) 32-BIT, 75 MHz, OTHER DSP, CBGA431 PDF資料下載

參數(shù)資料

| 型號: | MSC8102M4000 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | 32-BIT, 75 MHz, OTHER DSP, CBGA431 |

| 封裝: | 20 X 20 MM, FLIP CHIP, CERAMIC, BGA-431 |

| 文件頁數(shù): | 32/96頁 |

| 文件大小: | 1557K |

| 代理商: | MSC8102M4000 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁

2-8

AC Timings

2.6.4 System Bus Access Timing

2.6.4.1 Core Data Transfers

Generally, all MSC8102 bus and system output signals are driven from the rising edge of the reference

clock (REFCLK). The REFCLK is either the DLLIN signal or, if DLL is disabled, the CLKOUT signal.

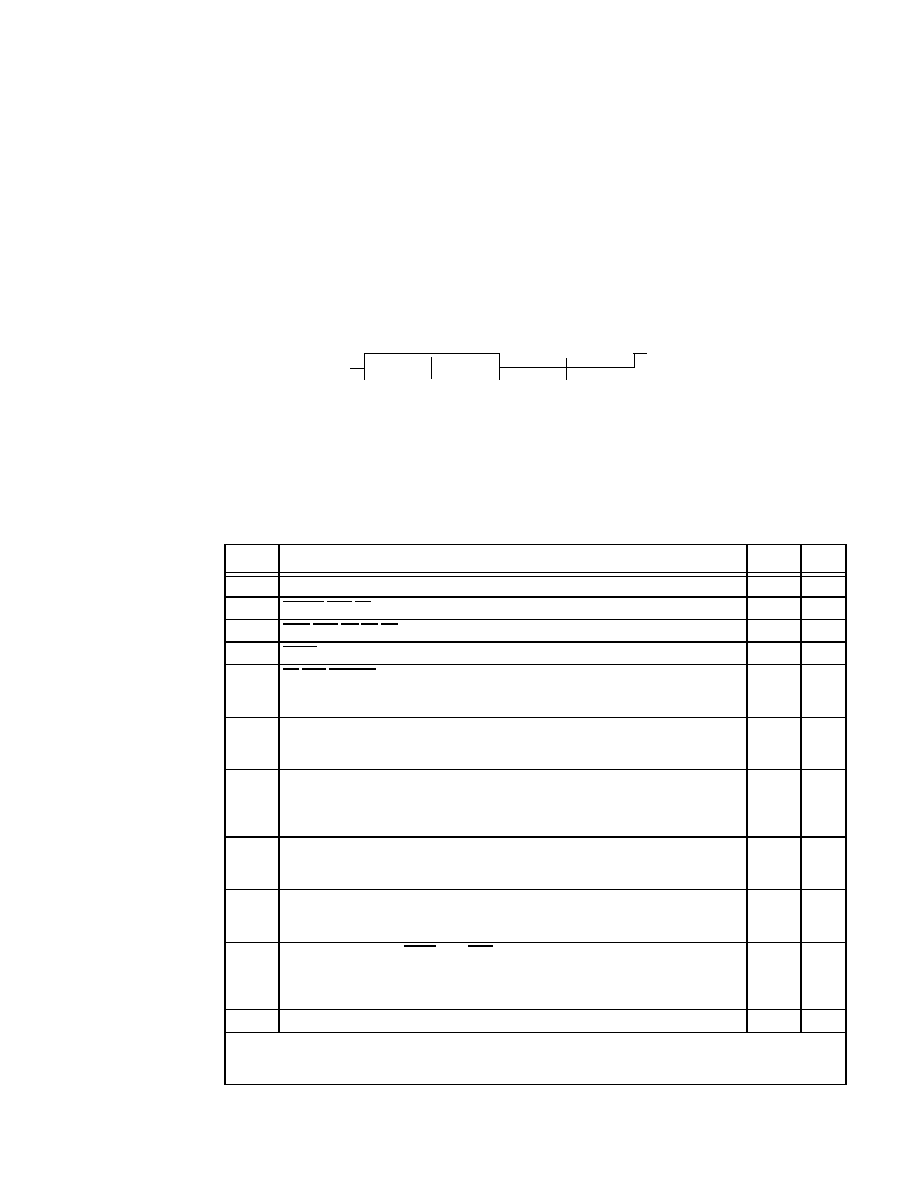

Memory controller signals, however, trigger on four points within a REFCLK cycle. Each cycle is

divided by four internal ticks: T1, T2, T3, and T4. T1 always occurs at the rising edge of REFCLK (and

T3 at the falling edge), as Figure 2-2 shows.

Figure 2-2 is a graphical representation of the internal ticks.

The UPM machine and GPCM machine outputs change on the internal tick determined by the memory

controller programming, the AC specifications are relative to the internal tick. SDRAM machine outputs

change only on the REFCLK rising edge.

Figure 2-2. Internal Tick Spacing for Memory Controller Signals

Table 2-11. AC Timing for SIU Inputs

No.

Characteristic

Value2 Units

10

Hold time for all signals after the 50% level of the REFCLK rising edge

1

ns

11a

ARTRY/ABB/TS setup time before the 50% level of the REFCLK rising edge

4.5

ns

11b

DBG/DBB/BG/BR/TC setup time before the 50% level of the REFCLK rising edge

4.5

ns

11c

AACK setup time before the 50% level of the REFCLK rising edge

5.0

ns

11d

TA/TEA/PSDVAL setup time before the 50% level of the REFCLK rising edge

Pipeline mode

Non-pipeline mode

4.5

5.0

ns

12

Data bus setup time before REFCLK rising edge in Normal mode

Pipeline mode

Non-pipeline mode

3.0

5.0

ns

13

Data bus setup time before the 50% level of the REFCLK rising edge in ECC and

PARITY modes

Pipeline mode

Non-pipeline mode

4

7

ns

14

DP setup time before the 50% level of the REFCLK rising edge

Pipeline mode

Non-pipeline mode

5.0

6.5

ns

15a

Address bus setup time before the 50% level of the REFCLK rising edge

Extra cycle mode (SIUBCR[EXDD] = 0)

No extra cycle mode (SIUBCR[EXDD] = 1)

4.0

8.0

ns

15b

Address attributes: TT/TBST/TSIZ/GBL setup time before the 50% level of the

REFCLK rising edge

Extra cycle mode (SIUBCR[EXDD] = 0)

No extra cycle mode (SIUBCR[EXDD] = 1)

6.0

9.0

ns

161

PUPMWAIT signal setup time before the 50% level of the REFCLK rising edge

5.0

ns

Notes:

1.

Synchronous operation. Asynchronous operation may have a higher setup time.

2.

Values are measured from the 50% TTL transition level relative to the 50% level of the REFCLK

rising edge.

REFCLK

T1

T2

T3

T4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MSC8122TVT6400 | 32-BIT, 400 MHz, OTHER DSP, PBGA431 |

| MSC8122TVT4800V | 32-BIT, 300 MHz, OTHER DSP, PBGA431 |

| MSC8122MP8000 | 32-BIT, 500 MHz, OTHER DSP, PBGA431 |

| MSC8144ETVT800B | 133 MHz, OTHER DSP, PBGA783 |

| MSC8144EVT1000A | 133 MHz, OTHER DSP, PBGA783 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MSC8102M4400 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad Core 16-Bit Digital Signal Processor |

| MSC8102RM | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad Core 16-Bit Digital Signal Processor |

| MSC8102UG | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Quad Core 16-Bit Digital Signal Processor |

| MSC8103 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Network Digital Signal Processor |

| MSC8103/D | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:Network Digital Signal Processor |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。