- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄67968 > MC68HLC705KJ1CDW (MOTOROLA INC) 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDSO16 PDF資料下載

參數(shù)資料

| 型號: | MC68HLC705KJ1CDW |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDSO16 |

| 封裝: | SOIC-16 |

| 文件頁數(shù): | 56/117頁 |

| 文件大小: | 1644K |

| 代理商: | MC68HLC705KJ1CDW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁

Central Processor Unit (CPU)

Instruction Set

MC68HC705KJ1MC68HRC705KJ1MC68HLC705KJ1 — Rev. 4.0

Data Sheet

MOTOROLA

Central Processor Unit (CPU)

43

4.6.2.2 Read-Modify-Write Instructions

These instructions read a memory location or a register, modify its contents, and

write the modified value back to the memory location or to the register.

NOTE:

Do not use read-modify-write instructions on registers with write-only bits.

4.6.2.3 Jump/Branch Instructions

Jump instructions allow the CPU to interrupt the normal sequence of the program

counter. The unconditional jump instruction (JMP) and the jump-to-subroutine

instruction (JSR) have no register operand. Branch instructions allow the CPU to

interrupt the normal sequence of the program counter when a test condition is met.

If the test condition is not met, the branch is not performed.

The BRCLR and BRSET instructions cause a branch based on the state of any

readable bit in the first 256 memory locations. These 3-byte instructions use a

combination of direct addressing and relative addressing. The direct address of the

byte to be tested is in the byte following the opcode. The third byte is the signed

offset byte. The CPU finds the effective branch destination by adding the third byte

to the program counter if the specified bit tests true. The bit to be tested and its

condition (set or clear) is part of the opcode. The span of branching is from –128

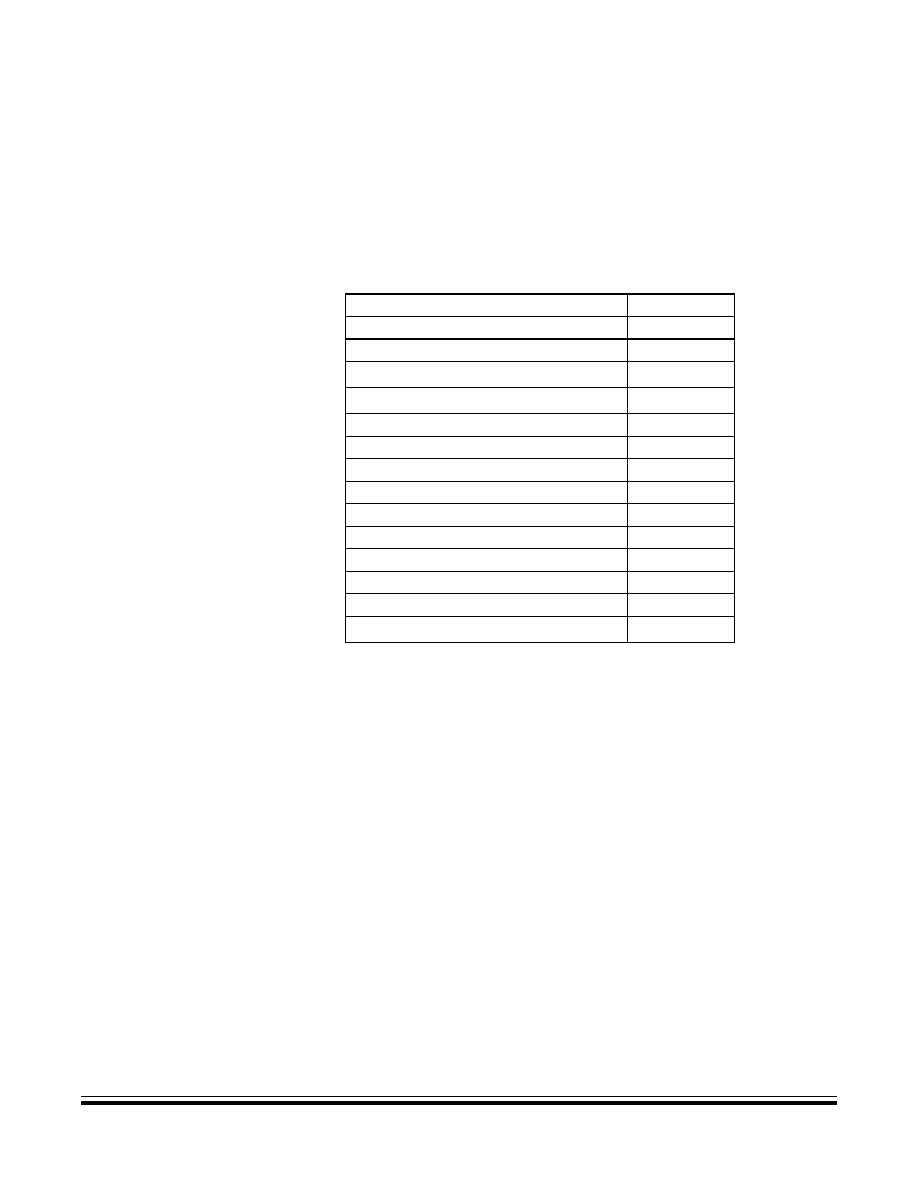

Table 4-2. Read-Modify-Write Instructions

Instruction

Mnemonic

Arithmetic Shift Left (Same as LSL)

ASL

Arithmetic Shift Right

ASR

Bit Clear

BCLR(1)

1. Unlike other read-modify-write instructions, BCLR and

BSET use only direct addressing.

Bit Set

BSET(1)

Clear Register

CLR

Complement (One’s Complement)

COM

Decrement

DEC

Increment

INC

Logical Shift Left (Same as ASL)

LSL

Logical Shift Right

LSR

Negate (Two’s Complement)

NEG

Rotate Left through Carry Bit

ROL

Rotate Right through Carry Bit

ROR

Test for Negative or Zero

TST(2)

2. TST is an exception to the read-modify-write sequence

because it does not write a replacement value.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68HC705KJ1CP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDIP16 |

| MC68HLC705KJ1CP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PDIP16 |

| MC7455ARX867LG | 32-BIT, 867 MHz, RISC PROCESSOR, CBGA483 |

| MC7445ARX733LG | 32-BIT, 733 MHz, RISC PROCESSOR, CBGA360 |

| MC7445ARX1000LG | 32-BIT, 1000 MHz, RISC PROCESSOR, CBGA360 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HLC908JK3CP | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT1CFQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT4CDW | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QT4CFQ | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MC68HLC908QY1CDW | 制造商:Rochester Electronics LLC 功能描述:LOW V-1.5K FLASH W/O ADC - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。