- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄98007 > M44C510-P40 (ATMEL CORP) 4-BIT, MROM, MICROCONTROLLER, PDIP40 PDF資料下載

參數(shù)資料

| 型號(hào): | M44C510-P40 |

| 廠商: | ATMEL CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 4-BIT, MROM, MICROCONTROLLER, PDIP40 |

| 封裝: | DIP-40 |

| 文件頁(yè)數(shù): | 36/57頁(yè) |

| 文件大小: | 1105K |

| 代理商: | M44C510-P40 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)

M44C510

TELEFUNKEN Semiconductors

Rev. A2, 13–Jan–98

41 (57)

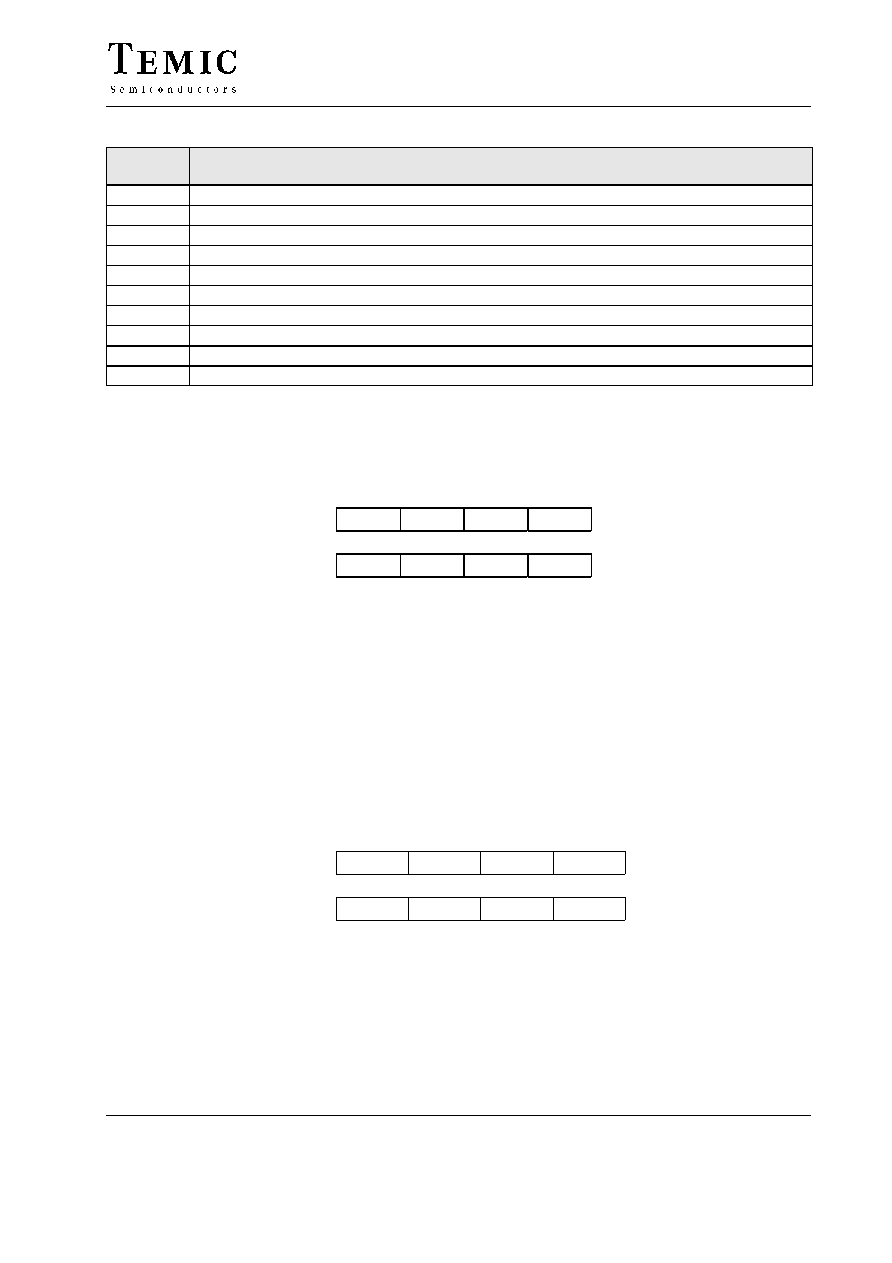

Table 20.Timer 1 Control Register (T1CR)

Code

3 2 1 0

Function

x x x 1

Timer 1 interrupt disabled

x x x 0

Timer 1 interrupt enabled

0 0 0 x

Timer 1 prescaler divide by 256

0 0 1 x

Timer 1 prescaler divide by 128

0 1 0 x

Timer 1 prescaler divide by 64

0 1 1 x

Timer 1 prescaler divide by 32

1 0 0 x

Timer 1 prescaler divide by 16

1 0 1 x

Timer 1 prescaler divide by 8

1 1 0 x

Timer 1 prescaler divide by 4

1 1 1 x

Timer 1 prescaler bypassed

Timer 1 Compare Register (T1CP) – Byte Write

Subport address (indirect write access): ’8’hex

Bit 3

Bit 2

Bit 1

Bit 0

T1CP

First write cycle

T1CP3

T1CP2

T1CP1

T1CP0

Reset value: xxxxb

Bit 7

Bit 6

Bit 5

Bit 4

Second write cycle

T1CP7

T1CP6

T1CP5

T1CP4

Reset value: xxxxb

T1CP3 ... T1CP0 – Timer 1 Compare Register Data (low nibble) – first write cycle

T1CP7. .. T1CP4 – Timer 1 Compare Register Data (high nibble) – second write cycle

The compare register T1CP is 8 bits wide and must be accessed as byte wide subport (see section “Addressing Peripher-

als”). The data is written low nibble first, followed by high nibble. Any timer interrupts are automatically suppressed

until the complete compare value has been transferred.

Timer 1 Capture Register (T1CA) – Byte Read

Subport address (indirect read access): ’8’hex

Bit 7

Bit 6

Bit 5

Bit 4

T1CA

First read cycle

T1CA7

T1CA6

T1CA5

T1CA4

Reset value: 0000b

Bit 3

Bit 2

Bit 1

Bit 0

Second read cycle

T1CA3

T1CA2

T1CA1

T1CA0

Reset value: 0000b

T1CA7 ... T1CA4 – Timer 1 Capture Register Data (high nibble) – first read cycle

T1CA3 ... T1CA0 – Timer 1 Capture Register Data (low nibble) – second read cycle

The 8-bit capture register T1CA is read as byte-wide subport. Note, however, unlike the writing to the compare register,

the high nibble is read first followed by low nibble. The 8-bit timer state is captured on reading the first nibble and held

until the complete byte has been read. During this transfer, the timer is free to continue counting.

Note: Halting the timer after a capture/compare interrupt event will reset the capture register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M44C510D-XXX-DOW | 4-BIT, MROM, MICROCONTROLLER |

| M44C588 | 4-BIT, MROM, 4 MHz, MICROCONTROLLER |

| M44C892 | 4-BIT, MROM, 4 MHz, MICROCONTROLLER, PDSO20 |

| M48T08Y-15PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

| M48T08Y-10PC1 | 0 TIMER(S), REAL TIME CLOCK, PDMA28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M44C890 | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44C890-H | 制造商:ATMEL 制造商全稱(chēng):ATMEL Corporation 功能描述:Low-Current Microcontroller for Wireless Communication |

| M44S05K4F1 | 功能描述:汽車(chē)連接器 MX44 Terminals RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類(lèi)型: 觸點(diǎn)電鍍:Nickel |

| M44T332538880MHZ | 制造商:MEC 功能描述: |

| M44T3338880MHZ | 制造商:MEC 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。