- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362742 > EP7209 (Cirrus Logic, Inc.) Ultra-Low-Power Audio Decoder System-on-Chip PDF資料下載

參數(shù)資料

| 型號: | EP7209 |

| 廠商: | Cirrus Logic, Inc. |

| 英文描述: | Ultra-Low-Power Audio Decoder System-on-Chip |

| 中文描述: | 超低功耗音頻解碼器系統(tǒng)級芯片 |

| 文件頁數(shù): | 61/128頁 |

| 文件大?。?/td> | 1382K |

| 代理商: | EP7209 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁當(dāng)前第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁

EP7209

DS453PP2

61

5.2.3

SYSCON3 System Control Register 3

ADDRESS: 0x8000eeg.2200

This register is an extension of SYSCON1 and SYSCON2, containing additional control for the

EP7209. The bits of this third system control register are defined in

Table 29

.

15

14

13

12

11

10

9

8

Reserved

7

VERSN[2]

Reserved

Reserved

6

VERSN[1]

Reserved

Reserved

5

VERSN[0]

Reserved

Reserved

4

ADCCKNSEN

Reserved

3

DAISEL

Reserved

2

CLKCTL1

DAIEN

1

CLKCTL0

FASTWAKE

0

ADCCON

Bit

0

ADCCON

: Determines whether the ADC Configuration Extension field SYNCIO(31:16) is to be

used for ADC configuration data. When this bit = 0 (default state) the ADC Configuration Byte

SYNCIO(7:0) only is used for compatibility with the CL-PS7111. When this bit = 1, the ADC Con-

figuration Extension field in the SYNCIO register is used for ADC Configuration data and the

value in the ADC Configuration Byte (SYNCIO(6:0)) selects the length of the data (8-bit to 16-bit).

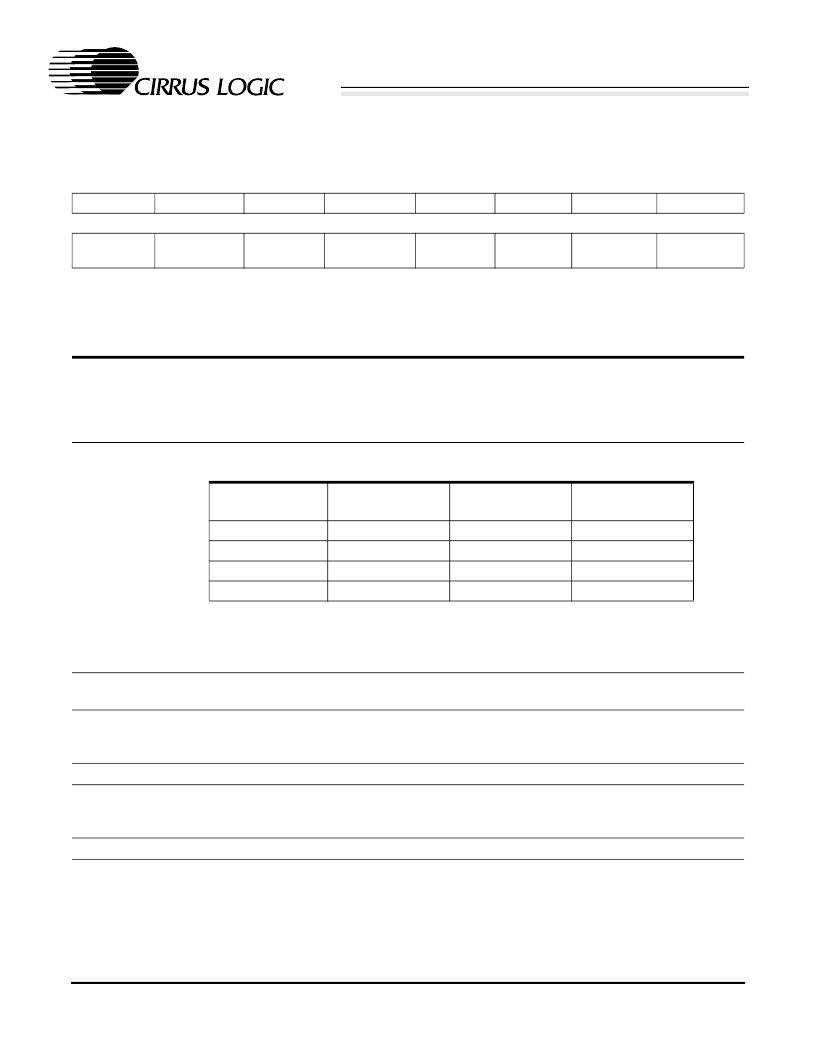

CLKCTL(1:0)

: Determines the frequency of operation of the processor and Wait State scaling.

The table below lists the available options.

1:2

NOTE:

To determine the number of wait states programmed refer to

Table 36

and

Table 37

.

When operating at 13 MHz, the CLKCTL[1:0] bits should not be changed from the

default value of

‘

00

’

. Under no circumstances should the CLKCTL bits be changed

using a buffered write.

DAIPSEL

: When set selects the DAI Interface. This defaults to either the SSI (i.e., DAISEL bit is

low).

ADCCKNSEN

: When set, configuration data is transmitted on ADCOUT at the rising edge of the

ADCCLK, and data is read back on the falling edge on the ADCIN pin. When clear (default), the

opposite edges are used.

VERSN[0:2]

: Additional read-only version bits

—

will read

‘

000

’

.

FASTWAKE

: When set, the device will wake from the Standby State within one to two cycles of a

4 kHz clock. This bit is cleared at power up, and thus the device first starts using the default one

to two cycles of the 8 Hz clock.

DAIEN

: This bit enables the Digital Audio Interface when set (i.e., when DAIEN is high).

3

4

5:7

8

9

Table 29. SYSCON3

CLKCTL(1:0)

Value

00

01

Processor

Frequency

18.432 MHz

36.864 MHz

Memory Bus

Frequency

18.432 MHz

36.864 MHz

Wait State

Scaling

1

2

10

11

49.152 MHz

73.728 MHz

36.864 MHz

36.864 MHz

2

2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP7211 | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CP-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7212 | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CB-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP7209-CB-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7209-CV-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7211 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211(208LQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211(256PBGA) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。