- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄362742 > EP7209 (Cirrus Logic, Inc.) Ultra-Low-Power Audio Decoder System-on-Chip PDF資料下載

參數(shù)資料

| 型號(hào): | EP7209 |

| 廠商: | Cirrus Logic, Inc. |

| 英文描述: | Ultra-Low-Power Audio Decoder System-on-Chip |

| 中文描述: | 超低功耗音頻解碼器系統(tǒng)級(jí)芯片 |

| 文件頁(yè)數(shù): | 40/128頁(yè) |

| 文件大小: | 1382K |

| 代理商: | EP7209 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)

EP7209

40

DS453PP2

The interface is fully capable of being clocked at

512 kHz when in slave mode. However, it is antic-

ipated that external hardware will be used to frame

the data into packets. Therefore, although the data

would be transmitted at a rate of 512 kbits/s, the

sustained data rate would in fact only be

85.3 kbits/s (i.e., 1 byte every 750

μ

sec). At this

data rate, the required interrupt rate will be greater

than 1 msec, which is acceptable.

There are separate half-word-wide RX and TX

FIFOs (16 half-words each) and corresponding in-

terrupts which are generated when the FIFO

’

s are

half-full or half-empty as appropriate. The inter-

rupts are called SS2RX and SS2TX, respectively.

Register SS2DR is used to access the FIFOs.

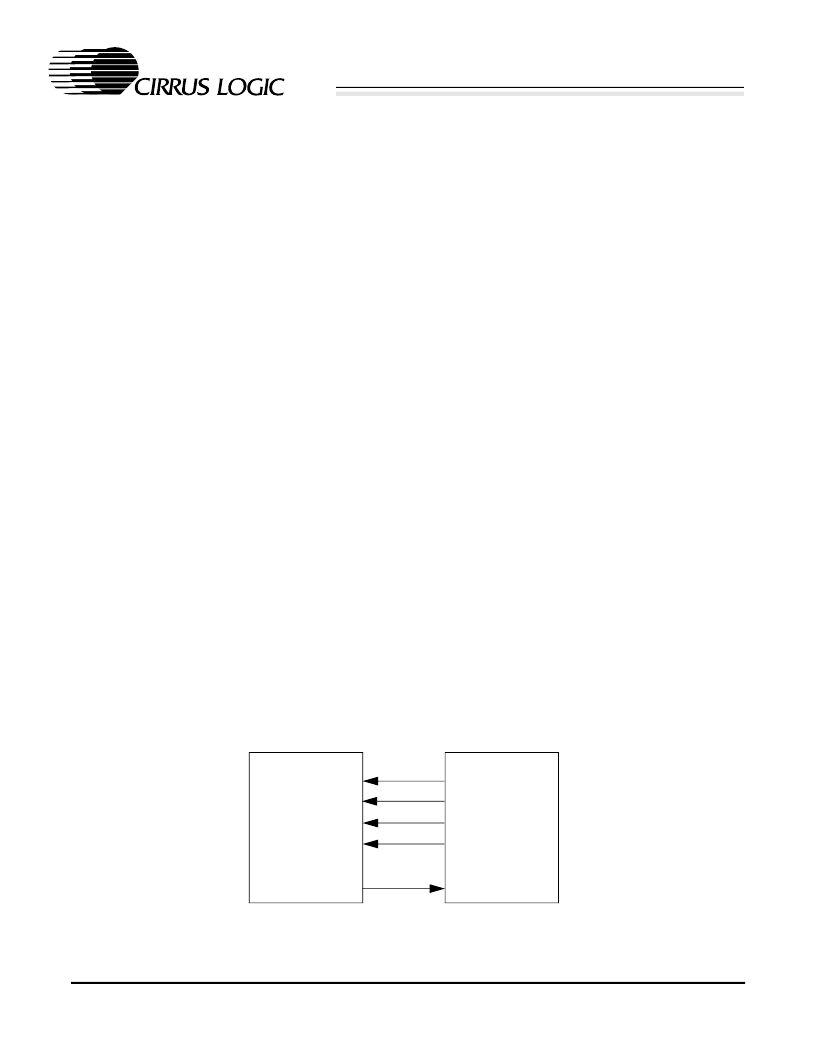

There are five pins to support this SSI port: SSIRX-

DA, SSITXFR, SSICLK, SSITXDA, and SSIRX-

FR. The SSICLK, SSIRXDA, SSIRXFR, and

SSITXFR signals are inputs and the SSITXDA sig-

nal is an output in slave mode. In the master mode,

SSICLK, SSITXDA, SSITXFR, and SSIRXFR are

outputs and SSIRXDA is an input. Master mode is

enabled by writing a one to the SS2MAEN bit

(SYSCON2[9]). When the master/slave SSI is not

required, it can be disabled to save power by writ-

ing a zero to the SS2TXEN and the SS2RXEN bits

(SYSCON2[4] [7]). When set, these two bits inde-

pendently enable the transmit and receive sides of

the interface.

The master/slave SSI is synchronous, full duplex,

and capable of supporting serial data transfers be-

tween two nodes. Although the interface is byte-

oriented, data is loaded in blocks of two bytes at a

time. Each data byte to be transferred is marked by

a frame sync pulse, lasting one clock period, and

located one clock prior to the first bit being trans-

ferred. Direction of the SSI2 ports, in slave and

master mode, is shown in

Figure 9

.

Data on the link is sent MSB first and coincides

with an appropriate frame sync pulse, of one clock

in duration, located one clock prior to the first data

bit sent (i.e., MSB). It is not possible to send data

LSB first.

When operating in master mode, the clock frequen-

cy is selected to be the same as the ADC interface

’

s

(master mode only SSI1)

—

that is, the frequencies

are selected by the same bits 16 and 17 of the

SYSCON1 register (i.e., the ADCKSEL bits).

Thus, the maximum frequency in master mode is

128 kbits/s. The interface will support continuous

transmission at this rate assuming that the OS can

respond to the interrupts within 1 msec to prevent

over/underruns.

Slave 7209

SSIRXFR

SSITXFR

SSICLK

SSIRXDA

SSITXDA

Master 7209

SSIRXFR

SSITXFR

SSICLK

SSITXDA

SSIRXDA

Figure 9. SSI2 Port Directions in Slave and Master Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP7211 | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CP-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211-CV-A | HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7212 | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

| EP7212-CB-A | HIGH-PERFORMANCE, LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER AND DIGITAL AUDIO INTERFACE(DAI) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP7209-CB-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7209-CV-D | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| EP7211 | 制造商:CIRRUS 制造商全稱:Cirrus Logic 功能描述:HIGH-PERFORMANCE ULTRA-LOW-POWER SYSTEM-ON-CHIP WITH LCD CONTROLLER |

| EP7211(208LQFP) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| EP7211(256PBGA) | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。