- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄1919 > ENC624J600T-I/PT (Microchip Technology)IC ETHERNET CTRLR W/SPI 64-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | ENC624J600T-I/PT |

| 廠商: | Microchip Technology |

| 文件頁(yè)數(shù): | 65/168頁(yè) |

| 文件大小: | 0K |

| 描述: | IC ETHERNET CTRLR W/SPI 64-TQFP |

| 視頻文件: | Fast 100 Mbps Ethernet PICtail Plus Overview |

| 標(biāo)準(zhǔn)包裝: | 1,200 |

| 控制器類(lèi)型: | 以太網(wǎng)控制器(IEEE 802.3) |

| 接口: | SPI |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 96mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類(lèi)型: | 表面貼裝 |

| 封裝/外殼: | 64-TQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 配用: | AC164132-ND - BOARD DAUGHTER PICTAIL ETHERNET |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)當(dāng)前第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)

2007 Microchip Technology Inc.

DS39599G-page 155

PIC18F2220/2320/4220/4320

17.0 MASTER SYNCHRONOUS

SERIAL PORT (MSSP)

MODULE

17.1

Master SSP (MSSP) Module

Overview

The Master Synchronous Serial Port (MSSP) module is

a serial interface useful for communicating with other

peripheral or microcontroller devices. These peripheral

devices may be serial EEPROMs, shift registers, dis-

play drivers, A/D converters, etc. The MSSP module

can operate in one of two modes:

Serial Peripheral Interface (SPI)

Inter-Integrated Circuit (I2C)

- Full Master mode

- Slave mode (with general address call)

The I2C interface supports the following modes in

hardware:

Master mode

Multi-Master mode

Slave mode

17.2

Control Registers

The MSSP module has three associated registers.

These include a status register (SSPSTAT) and two

control registers (SSPCON1 and SSPCON2). The use

of these registers and their individual Configuration bits

differ significantly, depending on whether the MSSP

module is operated in SPI or I2C mode.

Additional details are provided under the individual

sections.

17.3

SPI Mode

The SPI mode allows 8 bits of data to be synchronously

transmitted and received, simultaneously. All four

modes of SPI are supported. To accomplish

communication, typically three pins are used:

Serial Data Out (SDO) – RC5/SDO

Serial Data In (SDI) – RC4/SDI/SDA

Serial Clock (SCK) – RC3/SCK/SCL

Additionally, a fourth pin may be used when in a Slave

mode of operation:

Slave Select (SS) – RA5/AN4/SS/LVDIN/C2OUT

Register 17-1 shows the block diagram of the MSSP

module when operating in SPI mode.

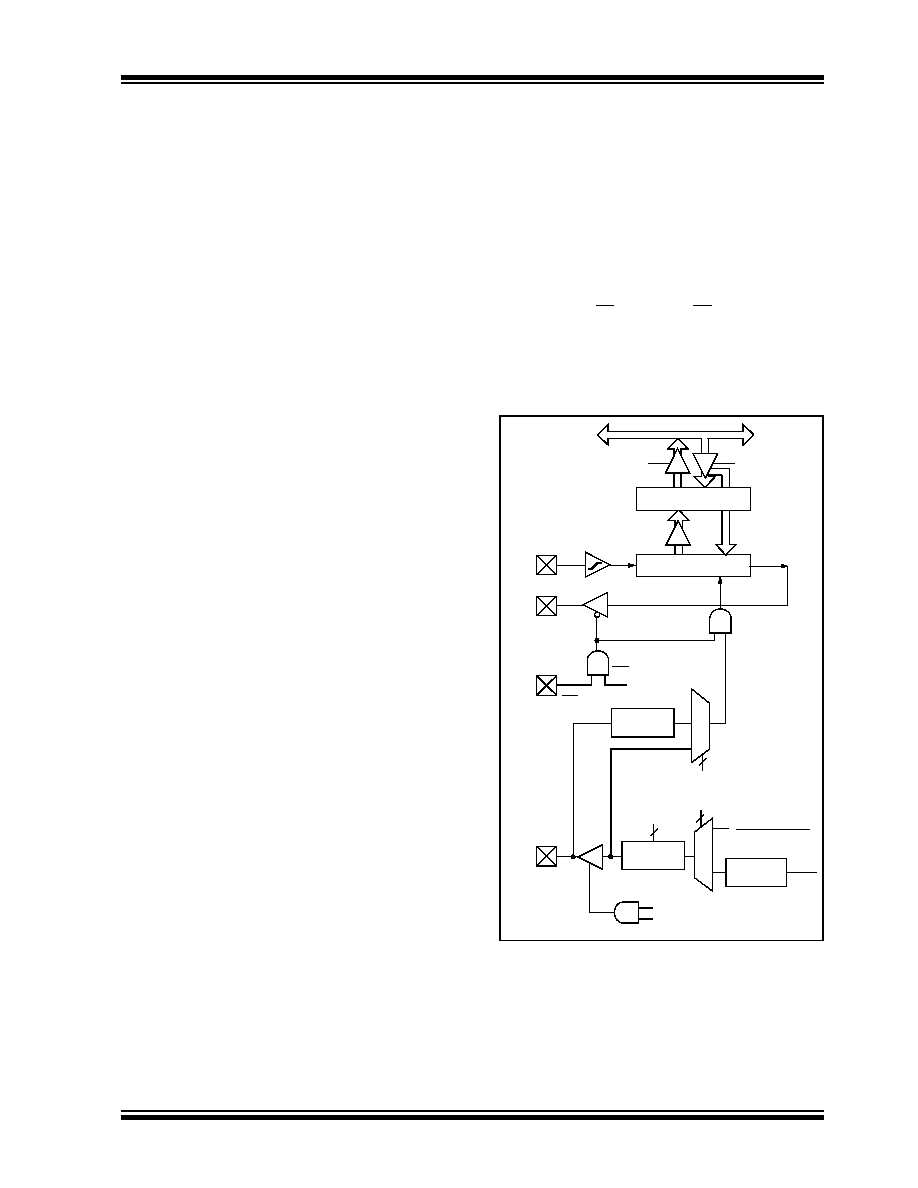

FIGURE 17-1:

MSSP BLOCK DIAGRAM

(SPI MODE)

(

)

Read

Write

Internal

Data Bus

SSPSR reg

SSPM3:SSPM0

bit 0

Shift

Clock

SS Control

Enable

Edge

Select

Clock Select

TMR2 Output

TOSC

Prescaler

4, 16, 64

2

Edge

Select

2

4

Data to TX/RX in SSPSR

TRIS bit

2

SMP:CKE

RC5/SDO

SSPBUF reg

RA5/AN4/SS/

RC3/SCK/

SCL

RC4/SDI/SDA

LVDIN/C2OUT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP1AGX90EF1152I6 | IC ARRIA GX FPGA 90K 1152FBGA |

| EP1C3T144A8N | IC CYCLONE FPGA 2910 LE 144-TQFP |

| EP1K100FC484-1N | IC ACEX 1K FPGA 100K 484-FBGA |

| EP1S80F1020C5N | IC STRATIX FPGA 80K LE 1020-FBGA |

| EP1SGX40GF1020I6 | IC STRATIX GX FPGA 40K 1020-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ENC680D05B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| ENC680D-05B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:STD MOV |

| ENC680D07B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

| ENC680D-07B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:STD MOV |

| ENC680D10B | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。