- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1919 > ENC624J600T-I/PT (Microchip Technology)IC ETHERNET CTRLR W/SPI 64-TQFP PDF資料下載

參數(shù)資料

| 型號: | ENC624J600T-I/PT |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 155/168頁 |

| 文件大小: | 0K |

| 描述: | IC ETHERNET CTRLR W/SPI 64-TQFP |

| 視頻文件: | Fast 100 Mbps Ethernet PICtail Plus Overview |

| 標準包裝: | 1,200 |

| 控制器類型: | 以太網(wǎng)控制器(IEEE 802.3) |

| 接口: | SPI |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 96mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-TQFP |

| 供應商設備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 配用: | AC164132-ND - BOARD DAUGHTER PICTAIL ETHERNET |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁當前第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁

2007 Microchip Technology Inc.

DS39599G-page 85

PIC18F2220/2320/4220/4320

8.0

8 X 8 HARDWARE MULTIPLIER

8.1

Introduction

An 8 x 8 hardware multiplier is included in the ALU of

the PIC18F2X20/4X20 devices. By making the multiply

a hardware operation, it completes in a single instruc-

tion cycle. This is an unsigned multiply that gives a

16-bit result. The result is stored into the 16-bit product

register pair (PRODH:PRODL). The multiplier does not

affect any flags in the STATUS register.

Making the 8 x 8 multiplier execute in a single-cycle

gives the following advantages:

Higher computational throughput

Reduces code size requirements for multiply

algorithms

The performance increase allows the device to be used

in applications previously reserved for Digital Signal

Processors.

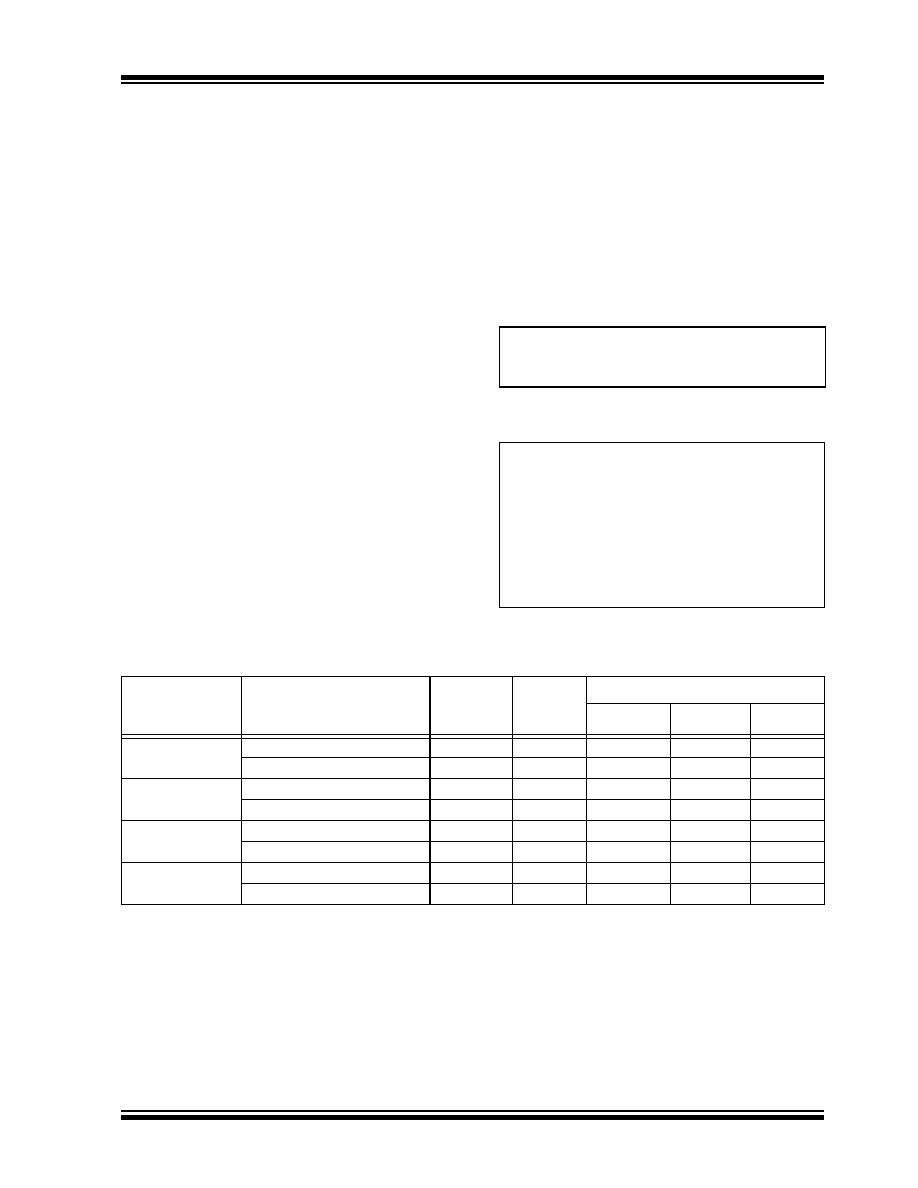

Table 8-1 shows a performance comparison between

enhanced devices using the single-cycle hardware

multiply and performing the same function without the

hardware multiply.

8.2

Operation

Example 8-1 shows the sequence to do an 8 x 8

unsigned multiply. Only one instruction is required

when one argument of the multiply is already loaded in

the WREG register.

Example 8-2 shows the sequence to do an 8 x 8 signed

multiply. To account for the sign bits of the arguments,

each argument’s Most Significant bit (MSb) is tested

and the appropriate subtractions are done.

EXAMPLE 8-1:

8 x 8 UNSIGNED

MULTIPLY ROUTINE

EXAMPLE 8-2:

8 x 8 SIGNED MULTIPLY

ROUTINE

TABLE 8-1:

PERFORMANCE COMPARISON

MOVF

ARG1, W

;

MULWF

ARG2

; ARG1 * ARG2 ->

;

PRODH:PRODL

MOVF

ARG1, W

MULWF

ARG2

; ARG1 * ARG2 ->

; PRODH:PRODL

BTFSC

ARG2, SB

; Test Sign Bit

SUBWF

PRODH, F

; PRODH = PRODH

;

- ARG1

MOVF

ARG2, W

BTFSC

ARG1, SB

; Test Sign Bit

SUBWF

PRODH, F

; PRODH = PRODH

;

- ARG2

Routine

Multiply Method

Program

Memory

(Words)

Cycles

(Max)

Time

@ 40 MHz

@ 10 MHz

@ 4 MHz

8 x 8 unsigned

Without hardware multiply

13

69

6.9

μs

27.6

μs

69

μs

Hardware multiply

1

100 ns

400 ns

1

μs

8 x 8 signed

Without hardware multiply

33

91

9.1

μs

36.4

μs

91

μs

Hardware multiply

6

600 ns

2.4

μs6 μs

16 x 16 unsigned

Without hardware multiply

21

242

24.2

μs

96.8

μs242 μs

Hardware multiply

28

2.8

μs11.2 μs28 μs

16 x 16 signed

Without hardware multiply

52

254

25.4

μs102.6 μs254 μs

Hardware multiply

35

40

4.0

μs

16.0

μs

40

μs

相關PDF資料 |

PDF描述 |

|---|---|

| EP1AGX90EF1152I6 | IC ARRIA GX FPGA 90K 1152FBGA |

| EP1C3T144A8N | IC CYCLONE FPGA 2910 LE 144-TQFP |

| EP1K100FC484-1N | IC ACEX 1K FPGA 100K 484-FBGA |

| EP1S80F1020C5N | IC STRATIX FPGA 80K LE 1020-FBGA |

| EP1SGX40GF1020I6 | IC STRATIX GX FPGA 40K 1020-FBGA |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| ENC680D05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D10B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。