- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄1919 > ENC624J600T-I/PT (Microchip Technology)IC ETHERNET CTRLR W/SPI 64-TQFP PDF資料下載

參數(shù)資料

| 型號(hào): | ENC624J600T-I/PT |

| 廠商: | Microchip Technology |

| 文件頁(yè)數(shù): | 133/168頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC ETHERNET CTRLR W/SPI 64-TQFP |

| 視頻文件: | Fast 100 Mbps Ethernet PICtail Plus Overview |

| 標(biāo)準(zhǔn)包裝: | 1,200 |

| 控制器類型: | 以太網(wǎng)控制器(IEEE 802.3) |

| 接口: | SPI |

| 電源電壓: | 3 V ~ 3.6 V |

| 電流 - 電源: | 96mA |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 64-TQFP |

| 供應(yīng)商設(shè)備封裝: | 64-TQFP(10x10) |

| 包裝: | 帶卷 (TR) |

| 配用: | AC164132-ND - BOARD DAUGHTER PICTAIL ETHERNET |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)當(dāng)前第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)

2007 Microchip Technology Inc.

DS21993C-page 65

PIC16CR7X

9.3

SSP I2C Operation

The SSP module in I2C mode fully implements all slave

functions except general call support, and provides

interrupts on Start and Stop bits in hardware to facilitate

firmware implementations of the master functions. The

SSP module implements the standard mode specifica-

tions as well as 7-bit and 10-bit addressing.

Two pins are used for data transfer. These are the RC3/

SCK/SCL pin, which is the clock (SCL), and the RC4/

SDI/SDA pin, which is the data (SDA). The user must

configure these pins as inputs or outputs through the

TRISC<4:3> bits.

The SSP module functions are enabled by setting SSP

enable bit SSPEN (SSPCON<5>).

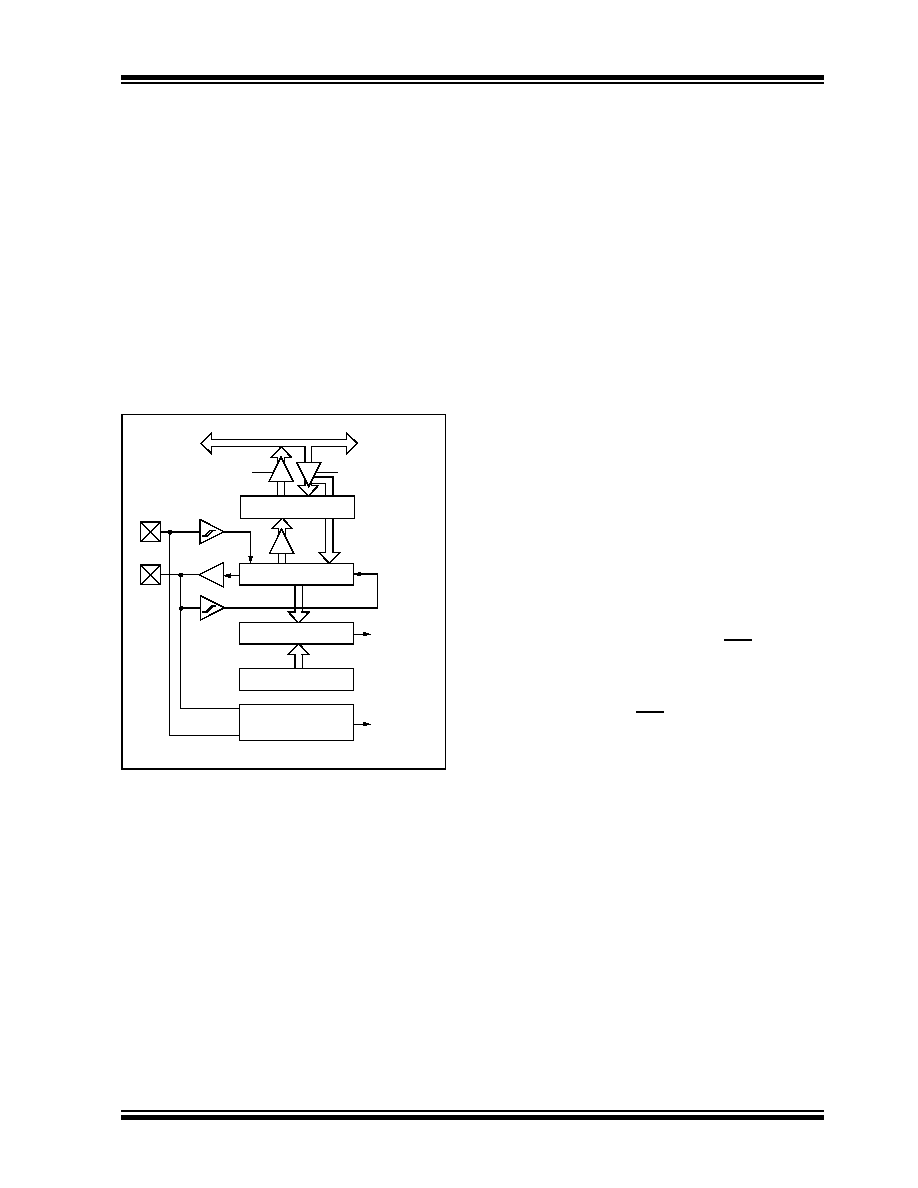

FIGURE 9-5:

SSP BLOCK DIAGRAM

(I2C MODE)

The SSP module has five registers for I2C operation.

These are the:

SSP Control Register (SSPCON)

SSP Status Register (SSPSTAT)

Serial Receive/Transmit Buffer (SSPBUF)

SSP Shift Register (SSPSR) – Not directly

accessible

SSP Address Register (SSPADD)

The SSPCON register allows control of the I2C opera-

tion. Four mode selection bits (SSPCON<3:0>) allow

one of the following I2C modes to be selected:

I2C Slave mode (7-bit address)

I2C Slave mode (10-bit address)

I2C Slave mode (7-bit address), with Start and

Stop bit interrupts enabled to support Firmware

Master mode

I2C Slave mode (10-bit address), with Start and

Stop bit interrupts enabled to support Firmware

Master mode

I2C Start and Stop bit interrupts enabled to

support Firmware Master mode, Slave is Idle

Selection of any I2C mode with the SSPEN bit set,

forces the SCL and SDA pins to be open drain, pro-

vided these pins are programmed to inputs by setting

the appropriate TRISC bits. Pull-up resistors must be

provided externally to the SCL and SDA pins for proper

operation of the I2C module.

Additional information on SSP I2C operation can be

found in the “PIC Mid-Range MCU Family Reference

Manual” (DS33023).

9.3.1

SLAVE MODE

In Slave mode, the SCL and SDA pins must be config-

ured as inputs (TRISC<4:3> set). The SSP module will

override the input state with the output data when

required (slave-transmitter).

When an address is matched, or the data transfer after

an address match is received, the hardware automati-

cally will generate the Acknowledge (ACK) pulse, and

then load the SSPBUF register with the received value

currently in the SSPSR register.

There are certain conditions that will cause the SSP

module not to give this ACK pulse. They include (either

or both):

a)

The Buffer Full bit BF (SSPSTAT<0>) was set

before the transfer was received.

b)

The overflow bit SSPOV (SSPCON<6>) was set

before the transfer was received.

In this case, the SSPSR register value is not loaded

into the SSPBUF, but bit SSPIF (PIR1<3>) is set.

Table 9-2 shows what happens when a data transfer

byte is received, given the status of bits BF and

SSPOV. The shaded cells show the condition where

user software did not properly clear the overflow condi-

tion. Flag bit BF is cleared by reading the SSPBUF

register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and

low for proper operation. The high and low times of the

I2C specification, as well as the requirements of the

SSP module, are shown in timing parameter #100 and

parameter #101.

Read

Write

SSPSR Reg

Match Detect

SSPADD Reg

Start and

Stop bit Detect

SSPBUF Reg

Internal

Data Bus

Addr Match

Set, Reset

S, P bits

(SSPSTAT Reg)

RC3/SCK/SCL

RC4/

Shift

Clock

MSb

SDI/

LSb

SDA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP1AGX90EF1152I6 | IC ARRIA GX FPGA 90K 1152FBGA |

| EP1C3T144A8N | IC CYCLONE FPGA 2910 LE 144-TQFP |

| EP1K100FC484-1N | IC ACEX 1K FPGA 100K 484-FBGA |

| EP1S80F1020C5N | IC STRATIX FPGA 80K LE 1020-FBGA |

| EP1SGX40GF1020I6 | IC STRATIX GX FPGA 40K 1020-FBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ENC680D05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-05B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| ENC680D-07B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:STD MOV |

| ENC680D10B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。