- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄379184 > DS80CH11 System Energy Manager PDF資料下載

參數(shù)資料

| 型號: | DS80CH11 |

| 英文描述: | System Energy Manager |

| 中文描述: | 系統(tǒng)能量管理器 |

| 文件頁數(shù): | 42/88頁 |

| 文件大?。?/td> | 598K |

| 代理商: | DS80CH11 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁

DS80CH11

011200 42/88

lowed by the transmission of the SEM’s slave address

with the direction bit set to 1. This byte will be shifted in

and loaded into the receive buffer register at the time the

acknowledge bit is returned to the master, resulting in

RXIx being set to 1. In addition, an address match

condition will occur as indicated by the ADMx flag

set to 1.

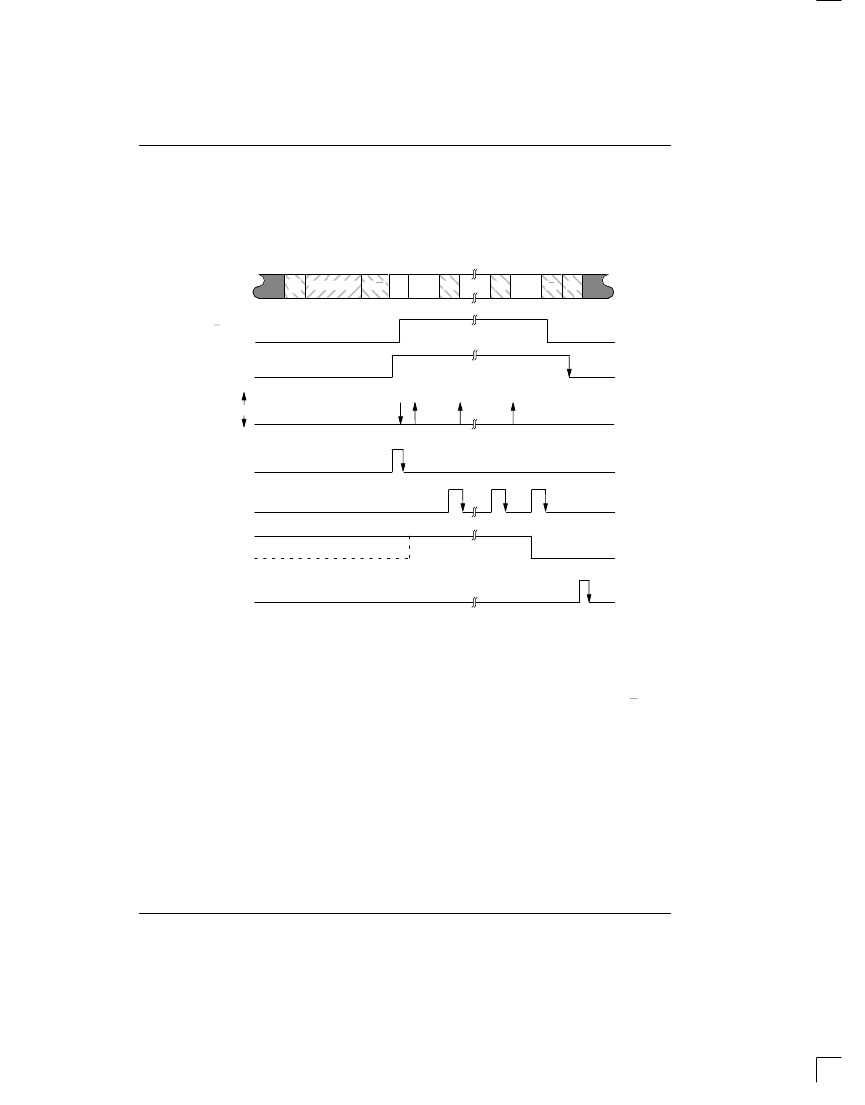

SLAVE TRANSMIT OPERATION TIMING

Figure 6–7

SDAx/SCLx

A

A

éé

éé

S

ADMx BIT

DATA BUF:

WRITE

READ

X/Rx BIT

RXIx BIT

TXIx BIT

ACKSx BIT

RSTOx BIT

Upon detecting these flags, the firmware should

respond by reading the receive buffer in order to deter-

mine if the programmed slave address or the general

call address was received. Following the read of the

buffer, the RXIx flag must be cleared. Also at this time

the firmware should insure that the 2WIFx bit is cleared

to 0, so that the interrupt flag will be set in response to

subsequent received data byte(s) and STOP condition.

If the programmed slave address was received, the

firmware can now send the first data byte by a write to

the transmit buffer. After the first data byte is transmitted

and the acknowledge bit received, the TXIx flag will be

set to 1. If the acknowledge bit ACKSx is returned as a

1, the next byte can be loaded into the transmit buffer

and the TXIx bit cleared. Successive bytes can be han-

dled in the same manner. Whenever any data is trans-

mitted from the 2–Wire port, the byte actually trans-

ferred on the bus will be shifted back in and loaded into

the receive buffer.

If the acknowledge bit ACKSx is returned as a 0 on a

transmitted byte, then the master is signaling this as the

last data byte in the packet. In this event, the X/Rx bit will

be automatically cleared to 0 and the firmware should

not write any more data bytes to the transmit buffer. The

TXIx bit must be cleared at this point by firmware; this

action will not cause any additional data to be sent since

the port is now in receive mode.

When the last byte of data has been sent, the bus mas-

ter will issue a STOP condition, which will result in the

RSTOx bit set to a 1. At this time, the port hardware

returns to the not–addressed slave mode.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS83C520 | EPROM/ROM High-Speed Micro |

| DS83C520-ECL | EPROM/ROM High-Speed Micro |

| DS83C520-ENL | EPROM/ROM High-Speed Micro |

| DS83C520-MCL | EPROM/ROM High-Speed Micro |

| DS83C520-MNL | EPROM/ROM High-Speed Micro |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS80CH11+E02 | 制造商:Maxim from Components Direct 功能描述:MAXIM DS80CH11+E02 SYSTEM ENERGY MANAGERS - Trays 制造商:Maxim 功能描述:Maxim DS80CH11+E02 System Energy Managers |

| DS80CH11-E02 | 制造商:Maxim from Components Direct 功能描述:MAXIM DS80CH11-E02 SYSTEM ENERGY MANAGERS - Trays 制造商:Maxim 功能描述:Maxim DS80CH11-E02 System Energy Managers |

| DS80E100 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:5 to 12.5 Gbps, Power-Saver Equalizer for Backplanes and Cables |

| DS80EP100 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:5 to 12.5 Gbps, Power-Saver Equalizer for Backplanes and Cables |

| DS80EP100_08 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:5 to 12.5 Gbps, Power-Saver Equalizer for Backplanes and Cables |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。