- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368876 > 24888 Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet PDF資料下載

參數(shù)資料

| 型號(hào): | 24888 |

| 英文描述: | Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet |

| 中文描述: | 初步的AMD - 8151 HyperTransport的AGP3.0圖形隧道數(shù)據(jù)表 |

| 文件頁數(shù): | 32/45頁 |

| 文件大?。?/td> | 755K |

| 代理商: | 24888 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

24888 Rev 3.02 - June 17, 2003

AMD-8151

TM

AGP Tunnel Data Sheet

32

Host-initiated transactions inside the windows are routed to the AGP bus.

PCI transactions initiated on the AGP bus inside the windows are not claimed by the IC.

Host initiated transactions outside the windows are passed through the tunnel or master aborted if the IC is at

the end of a HyperTransport technology chain.

PCI transactions initiated on the AGP bus outside the windows are claimed by the IC using medium decod-

ing and passed to the host.

So, for example, if IOBASE > IOLIM, then no host-initiated IO-space transactions are forwarded to the AGP

bus and all AGP-bus-initiated IO-space (not configuration) transactions are forwarded to the host. If MEM-

BASE > MEMLIM and PMEMBASE > PMEMLIM, then no host-initiated memory-space transactions are for-

warded to the AGP bus and all AGP-bus-initiated memory-space (not configuration) transactions are

forwarded to the host.

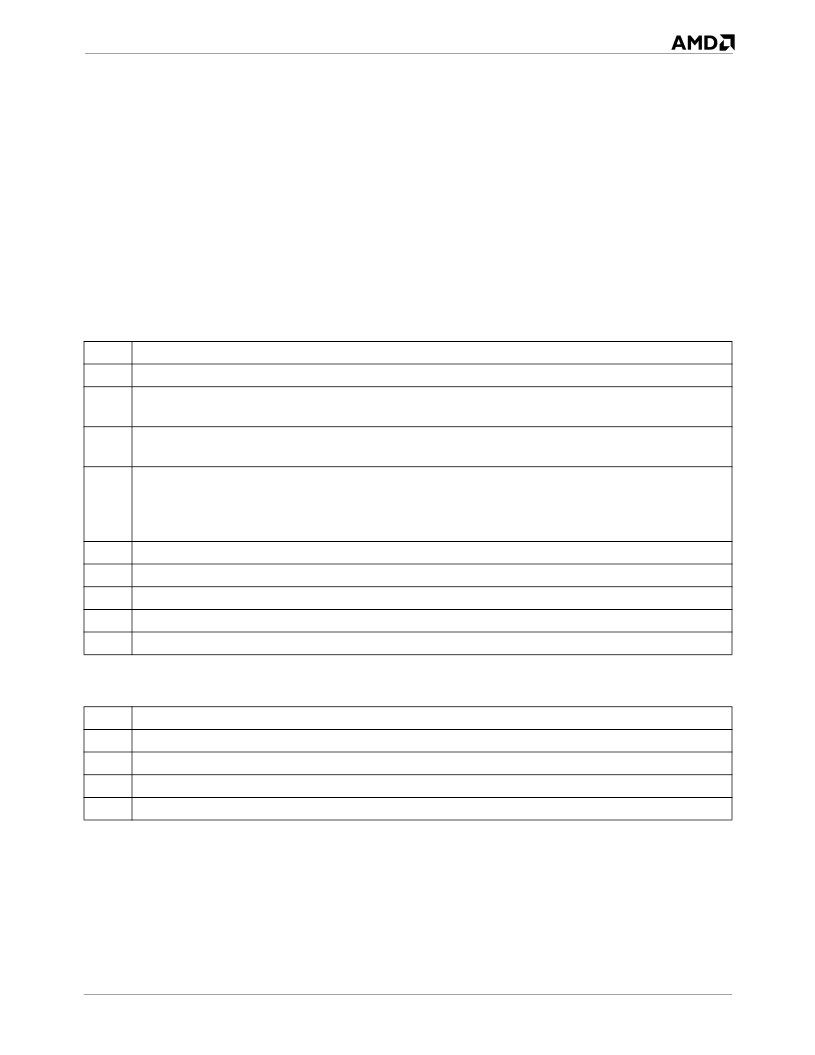

DevB:0x1C

. Default: 0220 01F1h

Bits

Description

31:30 Reserved.

29

RMA: received master abort.

Read; set by hardware; write 1 to clear. 1=The IC received a master

abort as a PCI master on the AGP bus. Note: this bit is cleared by PWROK reset but not by RESET#.

28

RTA: received target abort.

Read; set by hardware; write 1 to clear. 1=The IC received a target abort

as a PCI master on the AGP bus. Note: this bit is cleared by PWROK reset but not by RESET#.

27

STA: signaled target abort.

Read; set by hardware; write 1 to clear. 1=The IC generated a target

abort as a PCI target on the AGP bus. The IC generates target aborts if it receives a target abort (a non-

NXA error) response from the host to an AGP bus PCI master transaction request. Note: this bit is

cleared by PWROK reset but not by RESET#.

26:16 Read only. These bits are fixed in their default state.

15:12

IOLIM.

IO limit address bits[15:12]. See DevB:0x[30:1C] above.

11:8

Reserved.

7:4

IOBASE.

IO base address bits[15:12]. See DevB:0x[30:1C] above.

3:0

Reserved.

Attribute: See below.

DevB:0x20

. Default: 0000 FFF0h

Bits

Description

31:20

MEMLIM.

Non-prefetchable memory limit address bits[31:20]. See DevB:0x[30:1C] above.

19:16 Reserved.

15:4

MEMBASE.

Non-prefetchable memory base address bits[31:20]. See DevB:0x[30:1C] above.

3:0

Reserved.

Attribute: Read-write.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 249-151 | BEZEICHNUNGSKARTEN 1 BIS 16 |

| 249-152 | BEZEICHNUNGSKARTEN 17 BIS 32 |

| 249-161 | BEZEICHNUNGSSTREIFEN 1 16 |

| 249-162 | BEZEICHNUNGSSTREIFEN RASTER5 17 32 |

| 24919 | Incompatibilities Between the AMD-762? System Controller and the Via Technologies. Inc. VT82C686B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 248-8886-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8886-007 / 248-8886-007 / D Sub |

| 248-8887-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8887-007 / 248-8887-007 / D Sub |

| 248-8888-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8888-007 / 248-8888-007 / D Sub |

| 248-8889-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8889-007 / 248-8889-007 / D Sub |

| 248-8890-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8890-007 / 248-8890-007 / D SUB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。