- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368876 > 24888 Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet PDF資料下載

參數(shù)資料

| 型號: | 24888 |

| 英文描述: | Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet |

| 中文描述: | 初步的AMD - 8151 HyperTransport的AGP3.0圖形隧道數(shù)據(jù)表 |

| 文件頁數(shù): | 26/45頁 |

| 文件大?。?/td> | 755K |

| 代理商: | 24888 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當(dāng)前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

24888 Rev 3.02 - June 17, 2003

AMD-8151

TM

AGP Tunnel Data Sheet

26

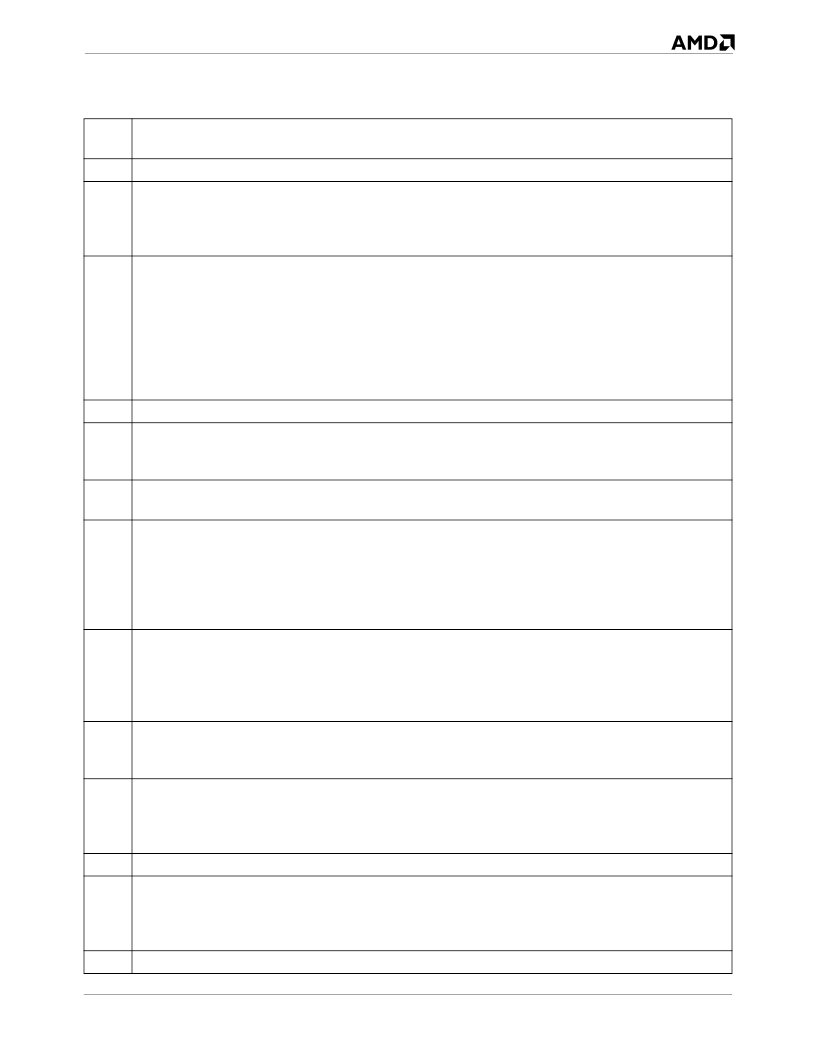

18:16

Max link width in.

Read only. This specifies the width of the incoming link to be 16 bits wide for

side A and 8 bits wide for side B.

15

Reserved.

14

EXTCTL: extended control time during initialization.

Read-write. This specifies the time in

which LT[B, A]CTL is held asserted during the initialization sequence that follows an LDTSTOP#

deassertion, after LR[B, A]CTL is detected asserted. 0=At least 16 bit times. 1=About 50

microseconds. Note: this bit is cleared by PWROK reset but not by RESET#.

13

LDT3SEN: link three-state enable.

Read-write. 1=During the LDTSTOP# disconnect sequence, the

link transmitter signals are placed into the high impedance state and the receivers are prepared for the

high impedance mode. For the receivers, this includes cutting power to the receiver differential

amplifiers and ensuring that there are no resultant high-current paths in the circuits. 0=During the

LDTSTOP# disconnect sequence, the link transmitter signals are driven, but in an undefined state,

and the link receiver signals are assumed to be driven. Note: this bit is cleared by PWROK reset but

not by RESET#. AMD recommends that this bit be set high in single-processor systems and be low in

multi-processor systems.

12:10 Reserved.

9:8

CRCERR: CRC Error.

Read; set by hardware; write 1 to clear. Bit[9] applies to the upper byte of

the link (DevA:0xC4 only) and bit[8] applies to the lower byte. 1=The hardware detected a CRC error

on the incoming link. Note: this bit is cleared by PWROK reset but not by RESET#.

7

TXOFF: transmitter off.

Read; write 1 only. 1=No output signals on the link toggle; the input link

receivers are disabled and the pins may float.

6

ENDOCH: end of chain.

Read; write 1 only or set by hardware. 1=The link is not part of the logical

HyperTransport technology chain; packets which are issued or forwarded to this link are either

dropped or result in an NXA error response, as appropriate; packets received from this link are

ignored and CRC is not checked; if the transmitter is still enabled (TXOFF), then it drives only NOP

packets with good CRC. ENDOCH may be set by writing a 1 to it or it may be set by hardware if the

link is determined to be disconnected at the rising edge of RESET#.

5

INITCPLT: initialization complete.

Read only. This bit is set by hardware when low-level link

initialization has successfully completed. If there is no device on the other end of the link, or if the

device on the other side of the link is unable to properly perform link initialization, then the bit is not

set. This bit is cleared when RESET# is asserted or after the link disconnect sequence completes after

the assertion of LDTSTOP#.

4

LKFAIL: link failure.

Read; set by hardware; write 1 to clear. This bit is set high by the hardware

when a CRC error is detected on the link (if enabled by CRCFEN) or if the link is not used in the

system. Note: this bit is cleared by PWROK reset, not by RESET#.

3

CRCERRCMD: CRC error command.

Read-write. 1=The link transmission logic generates

erroneous CRC values. 0=Transmitted CRC values match the values calculated per the link

specification. This bit is intended to be used to check the CRC failure detection logic of the device on

the other side of the link.

2

Reserved.

1

CRCFEN: CRC flood enable.

Read-write. 1=CRC errors (in link A for DevA:0xC4[CRCFEN]; in

link B for DevA:0xC8[CRCFEN]) result in sync packets to both outgoing links, DevA:0x04[SSE] is

set, and the LKFAIL bit is set. 0=CRC errors do not result in sync packets, setting of

DevA:0x04[SSE] or the LKFAIL bit.

0

Reserved.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 249-151 | BEZEICHNUNGSKARTEN 1 BIS 16 |

| 249-152 | BEZEICHNUNGSKARTEN 17 BIS 32 |

| 249-161 | BEZEICHNUNGSSTREIFEN 1 16 |

| 249-162 | BEZEICHNUNGSSTREIFEN RASTER5 17 32 |

| 24919 | Incompatibilities Between the AMD-762? System Controller and the Via Technologies. Inc. VT82C686B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 248-8886-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8886-007 / 248-8886-007 / D Sub |

| 248-8887-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8887-007 / 248-8887-007 / D Sub |

| 248-8888-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8888-007 / 248-8888-007 / D Sub |

| 248-8889-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8889-007 / 248-8889-007 / D Sub |

| 248-8890-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8890-007 / 248-8890-007 / D SUB |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。