- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄368876 > 24888 Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet PDF資料下載

參數(shù)資料

| 型號(hào): | 24888 |

| 英文描述: | Preliminary AMD-8151 HyperTransport AGP3.0 Graphics Tunnel Data Sheet |

| 中文描述: | 初步的AMD - 8151 HyperTransport的AGP3.0圖形隧道數(shù)據(jù)表 |

| 文件頁(yè)數(shù): | 22/45頁(yè) |

| 文件大小: | 755K |

| 代理商: | 24888 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)當(dāng)前第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)

24888 Rev 3.02 - June 17, 2003

AMD-8151

TM

AGP Tunnel Data Sheet

22

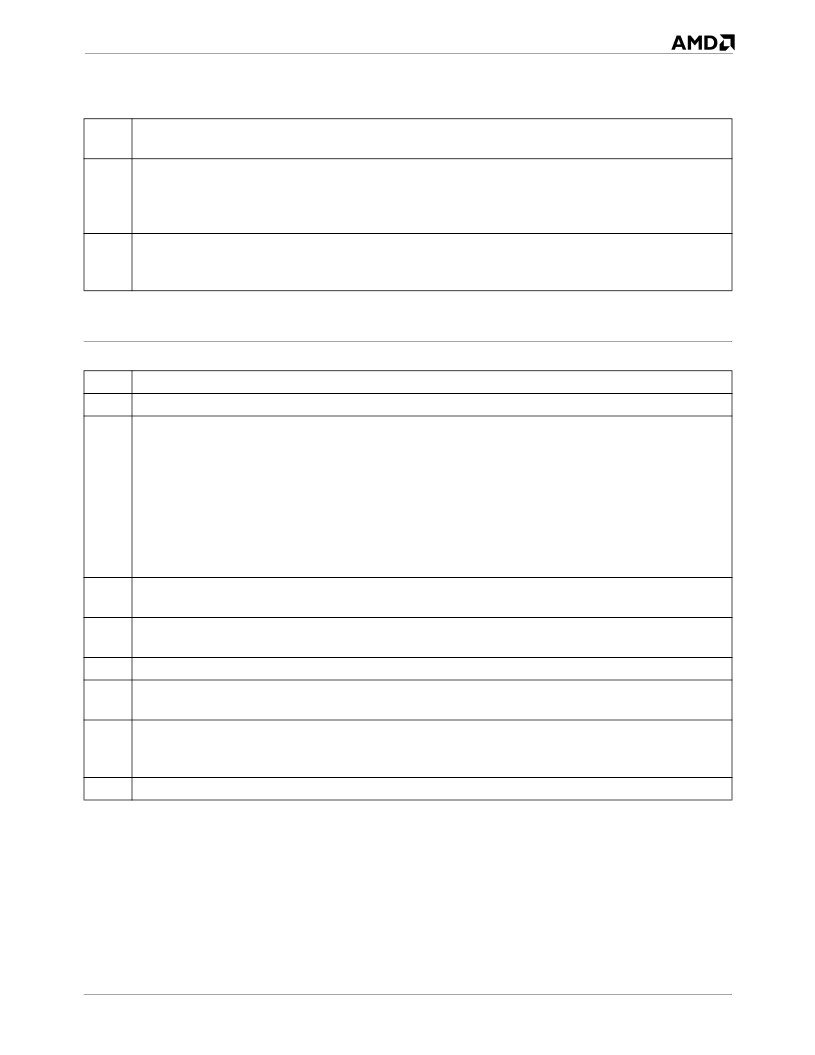

AGP Command Register

DevA:0xA8

Default: 0000 0000h

Bits

Description

31:13 Reserved.

12:10

PCALCYC: periodic calibration cycle.

Specifies the period between calibration cycles as follows:

000b=4 milliseconds; 001b=16 milliseconds; 010=64 milliseconds; 011b=256 milliseconds; all other

values are reserved. When DevA:0xA4[AGP3MD]=1, calibration cycles are as specified in the AGP

3.0 specification. When DevA:0xA4[AGP3MD]=0, calibration cycles consist of (1) the internal

calibration logic requests the bus; (2) once granted, the calibration values are update in less than 6

A_PCLK cycles while the AGP bus is in a quiescent state. Note: after changing this value, the IC may

not perform another calibration cycle until the internal counter rolls over as much as 256

microseconds later; in order to avoid this, DevA:0xB0[CALDIS] should be set high before changing

PCALCYC and then DevA:0xB0[CALDIS] should be cleared afterward.

9

SBA_EN: side band address enable.

1=SBA addressing is enabled. Note: when

DevA:0xA4[AGP3MD]=1, SBA addressing is enabled and the state of this bit is ignored.

8

AGPEN: AGP operation enable.

1=The IC accepts master-initiated AGP commands. 0=AGP

commands are ignored.

7:6

Reserved.

5

R4GEN: receive greater-than 4-gigabyte access enable.

1=The IC accepts AGP accesses to

addresses greater than 4 gigabytes.

4

FWEN: fast write enable.

1=Fast writes are enabled. When DevA:0xA4[FWSUP]=0, this bit is

required to be programmed low; if, in this case, this bit is programmed high, then undefined behavior

results.

3

Reserved.

Attribute: Read-write.

4

FWSUP: fast write support flag.

0=Fast writes are not supported. 1=Fast writes are supported. The

state of this bit is controlled by DevA:0x40[FWDIS].

AGP3MD: AGP 3.0 signaling mode detected.

1=The IC detected connection to an AGP 3.0-capable

master and is programmed for AGP 3.0 signaling. 0=The IC detected connection to an AGP 2.0 or

earlier capable master or is not programmed for 1.5-volt, AGP 2.0 signaling. If

DevA:0x40[8XDIS]=0 and the pin A_GC8XDET#=0, then this bit is high. Otherwise, it is low.

RATE: data rate.

When AGP3MD=1, then this field defaults to 011b to indicate support for 4x and

8x data rates. When AGP3MD=0, this field defaults to 111b to indicate support for 4x, 2x, and 1x data

rates.

3

2:0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 249-151 | BEZEICHNUNGSKARTEN 1 BIS 16 |

| 249-152 | BEZEICHNUNGSKARTEN 17 BIS 32 |

| 249-161 | BEZEICHNUNGSSTREIFEN 1 16 |

| 249-162 | BEZEICHNUNGSSTREIFEN RASTER5 17 32 |

| 24919 | Incompatibilities Between the AMD-762? System Controller and the Via Technologies. Inc. VT82C686B |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 248-8886-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8886-007 / 248-8886-007 / D Sub |

| 248-8887-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8887-007 / 248-8887-007 / D Sub |

| 248-8888-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8888-007 / 248-8888-007 / D Sub |

| 248-8889-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8889-007 / 248-8889-007 / D Sub |

| 248-8890-007 | 制造商:ITT Interconnect Solutions 功能描述:248-8890-007 / 248-8890-007 / D SUB |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。