- 您現在的位置:買賣IC網 > PDF目錄385641 > MT9VDDT1672A (Micron Technology, Inc.) DDR SDRAM DIMM PDF資料下載

參數資料

| 型號: | MT9VDDT1672A |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | DDR SDRAM DIMM |

| 中文描述: | DDR SDRAM的內存 |

| 文件頁數: | 25/29頁 |

| 文件大?。?/td> | 542K |

| 代理商: | MT9VDDT1672A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當前第25頁第26頁第27頁第28頁第29頁

128MB, 256MB (x72, ECC)

184-Pin DDR SDRAM DIMM

09005aef808f8ccd

DD9C16_32X72AG_B.fm - Rev. B 2/03 EN

Micron Technology, Inc., reserves the right to change products or specifications without notice.

25

2003 Micron Technology. Inc.

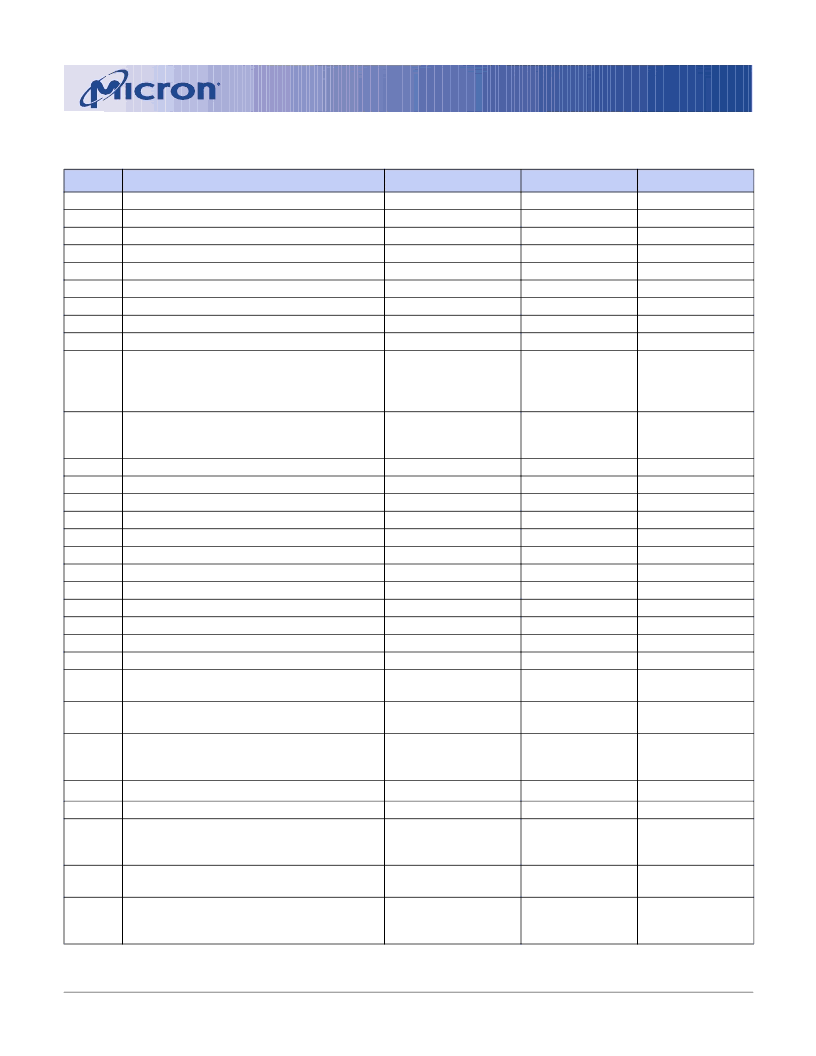

Table 20: Serial Presence-Detect Matrix

“1”/“0”: Serial Data, “driven to HIGH”/“driven to LOW”; notes at end of SPD Matrix

BYTE

0

1

2

3

4

5

6

7

8

9

DESCRIPTION

ENTRY (VERSION)

128

256

SDRAM DDR

12 or 13

10

1

72

0

SSTL 2.5V

6ns (-335)

7ns (-262/-26A)

7.5ns (-265)

8ns (-202)

0.7ns (-335)

0.75ns (-262/-265/-26A)

0.8ns (-202)

ECC

15.6 or 7.81μs/SELF

8

8

1

MT9VDDT1672A

80

08

07

0C

0A

01

48

00

04

60

70

75

80

70

75

80

02

80

08

08

01

MT9VDDT3272A

80

08

07

0D

0A

01

48

00

04

60

70

75

80

70

75

80

02

82

08

08

01

Number of Bytes Used by Micron

Total Number of SPD Memory Bytes

Memory Type

Number of Row Addresses

Number of Column Addresses

Number of Ranks

Module Data Width

Module Data Width (Continued)

Module Voltage Interface Levels

SDRAM Cycle Time,

t

CK, (CAS Latency = 2.5)

(See note 1)

10

SDRAM Access From Clock,

t

AC

(CAS Latency = 2.5)

11

12

13

14

15

Module Configuration Type

Refresh Rate/Type

SDRAM Width (Primary SDRAM)

Error-Checking SDRAM Data Width

Minimum Clock Delay, Back -to- Back

Random Column Access

Burst Lengths Supported

Number of Banks on SDRAM Device

CAS Latencies Supported

CS Latency

WE Latency

SDRAM Module Attributes

SDRAM Device Attributes: General

16

17

18

19

20

21

22

2, 4, 8

4

2, 2.5

0

1

0E

04

0C

01

02

20

0E

04

0C

01

02

20

C0

Unbuffered, Diff CLK

Fast/concurrent auto

precharge

7.5ns (-335/-262/-26A)

10ns (-202/-265)

0.7ns (-335)

0.75ns (-262/-265/-26A)

0.8ns (-202)

–

00/C0

(See note 2)

75

A0

70

75

80

00

23

SDRAM Cycle Time,

t

CK (CAS Latency = 2)

75

A0

70

75

80

00

24

SDRAM Cycle Time,

t

CK (CAS Latency = 2)

(See note 1)

25

SDRAM Cycle Time,

t

CK (CAS Latency = 1)

SDRAM Access From CK , (CAS latency = 1)

Minimum Row Precharge Time,

t

RP

26

27

–

00

48

3C

50

30

3C

48

3C

50

00

48

3C

50

30

3C

48

3C

50

18ns (-335)

20ns (-262)

20ns (-202/-265/-26A)

12ns (-335)

15ns (-202/-265/-26A)/-262

18ns (-335)

20ns (-262)

20ns (-202/-265/-26A)

28

Minimum Row Active To Row Active,

t

RRD

29

Minimum RAS# to CAS# Delay,

t

RCD

相關PDF資料 |

PDF描述 |

|---|---|

| MT9VDDT3272A | DDR SDRAM DIMM |

| MTB2P50E | Power MOSFET 2 Amps, 500 Volts(2A, 500V功率MOSFET) |

| MTB50P03HDL | Power MOSFET 50 Amps, 30 Volts, Logic Level(50A, 30V, D2PAK, P溝道功率MOSFET) |

| MTD20N06HDLT4 | Power MOSFET 20 Amps, 60 Volts, Logic Level N−Channel DPAK |

| MTD20N06HDLT4G | Power MOSFET 20 Amps, 60 Volts, Logic Level N−Channel DPAK |

相關代理商/技術參數 |

參數描述 |

|---|---|

| MT9VDDT1672AG-202A1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-265B1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-265D4 | 制造商:Micron Technology Inc 功能描述: |

| MT9VDDT1672AG-26AA1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-26AB1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復。