- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385641 > MT9VDDT1672A (Micron Technology, Inc.) DDR SDRAM DIMM PDF資料下載

參數(shù)資料

| 型號(hào): | MT9VDDT1672A |

| 廠商: | Micron Technology, Inc. |

| 英文描述: | DDR SDRAM DIMM |

| 中文描述: | DDR SDRAM的內(nèi)存 |

| 文件頁數(shù): | 14/29頁 |

| 文件大小: | 542K |

| 代理商: | MT9VDDT1672A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

128MB, 256MB (x72, ECC)

184-Pin DDR SDRAM DIMM

09005aef808f8ccd

DD9C16_32X72AG_B.fm - Rev. B 2/03 EN

Micron Technology, Inc., reserves the right to change products or specifications without notice.

14

2003 Micron Technology. Inc.

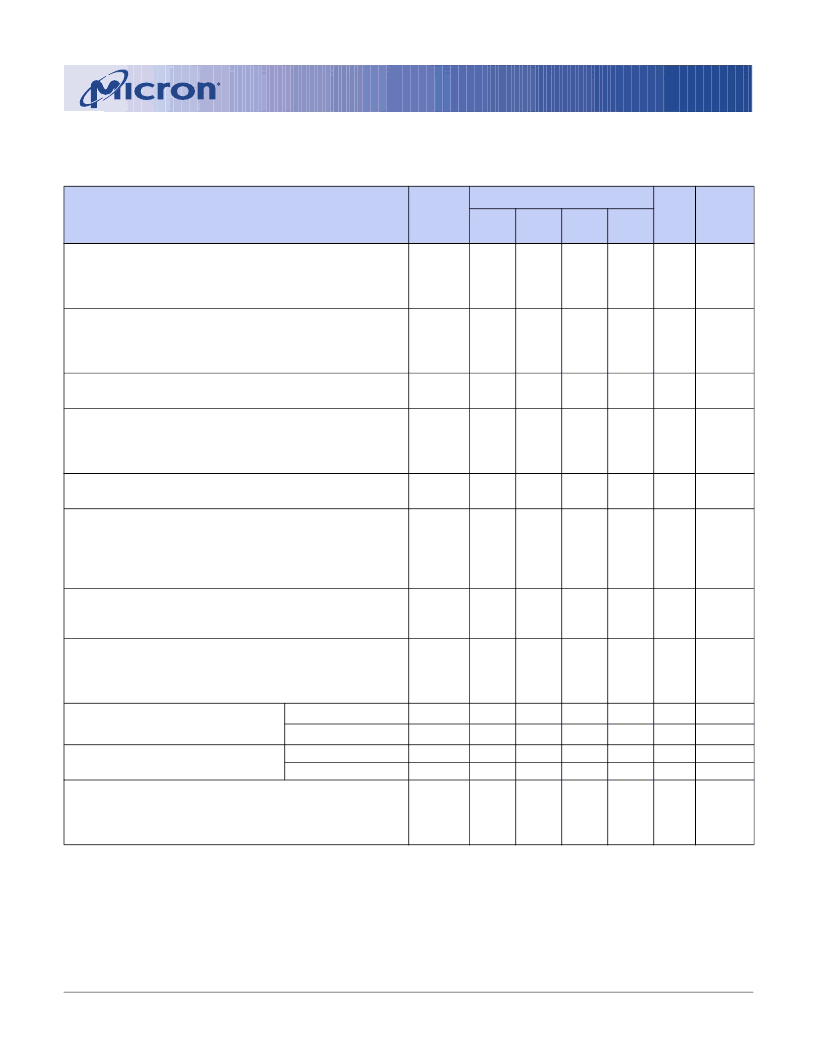

Table 12: I

DD

Specifications and Conditions (128MB)

DRAM components only

Notes: 1–5, 8, 10, 12, 50; notes appear on pages 18–21; 0 C T

A

+70 C; V

DD

= V

DD

Q = +2.5V +0.2V

PARAMETER/CONDITION

SYMBOL

I

DD

0

MAX

UNITS

mA

NOTES

20, 43

-335

TBD

-262

TBD

-26A/

-265

945

-202

900

OPERATING CURRENT: One device bank; Active-Precharge;

t

RC =

t

RC (MIN);

t

CK =

t

CK (MIN); DQ, DM, and DQS inputs

changing once per clock cycle; Address and control inputs

changing once every two clock cycles;

OPERATING CURRENT: One device bank; Active-Read-

Precharge; Burst = 2;

t

RC =

t

RC (MIN);

t

CK =

t

CK (MIN); I

OUT

=

0mA; Address and control inputs changing once per clock

cycle

PRECHARGE POWER-DOWN STANDBY CURRENT: All device

banks idle; Power-down mode;

t

CK =

t

CK (MIN); CKE = LOW;

IDLE STANDBY CURRENT: CS# = HIGH; All device banks idle;

t

CK =

t

CK (MIN); CKE = HIGH; Address and other control

inputs changing once per clock cycle. V

IN

= V

REF

for DQ, DQS,

and DM

ACTIVE POWER-DOWN STANDBY CURRENT: One device bank

active; Power-down mode;

t

CK =

t

CK (MIN); CKE = LOW

ACTIVE STANDBY CURRENT: CS# = HIGH; CKE = HIGH; One

device bank; Active-Precharge;

t

RC =

t

RAS (MAX);

t

CK =

t

CK

(MIN); DQ, DM, and DQS inputs changing twice per clock

cycle; Address and other control inputs changing once per

clock cycle

OPERATING CURRENT: Burst = 2; Reads; Continuous burst;

One device bank active; Address and control inputs changing

once per clock cycle;

t

CK =

t

CK (MIN); I

OUT

= 0mA

OPERATING CURRENT: Burst = 2; Writes; Continuous burst;

One device bank active; Address and control inputs changing

once per clock cycle;

t

CK =

t

CK (MIN); DQ, DM, and DQS

inputs changing twice per clock cycle

AUTO REFRESH CURRENT

I

DD

1

TBD

TBD

1,080

990

mA

20, 43

I

DD

2

P

TBD

TBD

27

27

mA

21, 28, 45

I

DD

2

F

TBD

TBD

405

315

mA

46

I

DD

3

P

TBD

TBD

180

180

mA

21, 28, 45

I

DD

3

N

TBD

TBD

405

315

mA

40

I

DD

4

R

TBD

TBD

1,125

945

mA

20, 43,

24, 45

I

DD

4

W

TBD

TBD

1,035

945

mA

20

t

RC =

t

RFC (MIN)

t

RC = 15.625μs

Standard

Low Power

I

DD

5

TBD

TBD

1,890

1,845

mA

24, 45

I

DD

5A

TBD

TBD

45

45

mA

24, 45

SELF REFRESH CURRENT: CKE 0.2V

I

DD

6

I

DD

6A

I

DD

7

TBD

TBD

TBD

TBD

TBD

TBD

18

9

18

9

mA

mA

mA

9

OPERATING CURRENT: Four device bank interleaving READs

(BL=4) with auto precharge,

t

RC =

t

RC (MIN);

t

CK =

t

CK (MIN);

Address and control inputs change only during Active, READ,

or WRITE commands.

2,925

2,475

20, 44

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9VDDT3272A | DDR SDRAM DIMM |

| MTB2P50E | Power MOSFET 2 Amps, 500 Volts(2A, 500V功率MOSFET) |

| MTB50P03HDL | Power MOSFET 50 Amps, 30 Volts, Logic Level(50A, 30V, D2PAK, P溝道功率MOSFET) |

| MTD20N06HDLT4 | Power MOSFET 20 Amps, 60 Volts, Logic Level N−Channel DPAK |

| MTD20N06HDLT4G | Power MOSFET 20 Amps, 60 Volts, Logic Level N−Channel DPAK |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9VDDT1672AG-202A1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-265B1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-265D4 | 制造商:Micron Technology Inc 功能描述: |

| MT9VDDT1672AG-26AA1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

| MT9VDDT1672AG-26AB1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD DDR SDRAM 1.125GBIT 184UDIMM - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。