- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄69032 > MCIMX537CVV8C (FREESCALE SEMICONDUCTOR INC) 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 PDF資料下載

參數(shù)資料

| 型號: | MCIMX537CVV8C |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 800 MHz, RISC PROCESSOR, PBGA529 |

| 封裝: | 19 X 19 MM, 0.80 MM PITCH, ROHS COMPLIANT, PLASTIC, TEPBGA-529 |

| 文件頁數(shù): | 164/172頁 |

| 文件大小: | 4562K |

| 代理商: | MCIMX537CVV8C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁當(dāng)前第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁

Electrical Characteristics

i.MX53 Applications Processors for Industrial Products, Rev. 3

Freescale Semiconductor

91

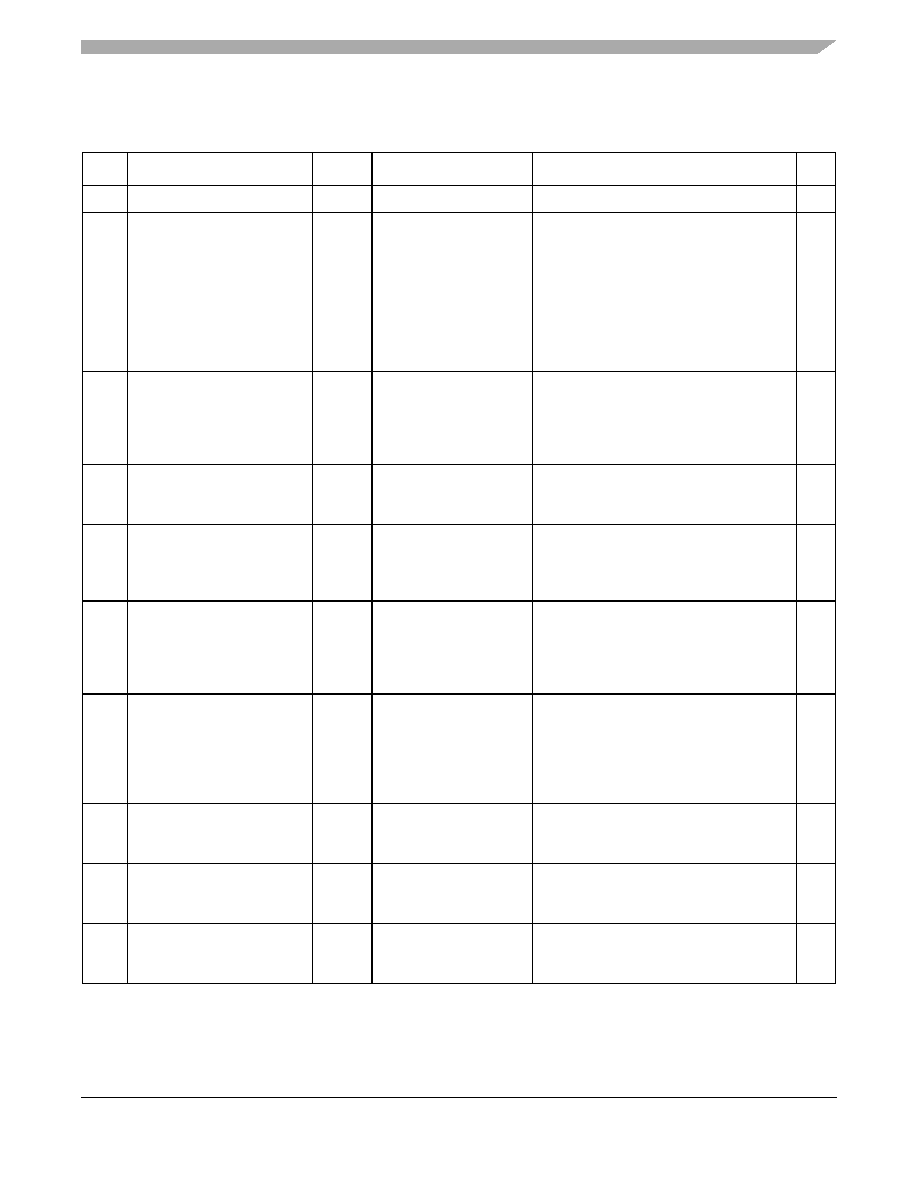

Table 60. Synchronous Display Interface Timing Characteristics (Pixel Level)

ID

Parameter

Symbol

Value

Description

Unit

IP5

Display interface clock period

Tdicp

(1)

Display interface clock. IPP_DISP_CLK

ns

IP6

Display pixel clock period

Tdpcp

DISP_CLK_PER_PIXEL

× Tdicp

Time of translation of one pixel to display,

DISP_CLK_PER_PIXEL—number of pixel

components in one pixel (1.n). The

DISP_CLK_PER_PIXEL is virtual

parameter to define Display pixel clock

period.

The DISP_CLK_PER_PIXEL is received by

DC/DI one access division to n

components.

ns

IP7

Screen width time

Tsw

(SCREEN_WIDTH)

× Tdicp

SCREEN_WIDTH—screen width in,

interface clocks. horizontal blanking

included.

The SCREEN_WIDTH should be built by

suitable DI’s counter2.

ns

IP8

HSYNC width time

Thsw

(HSYNC_WIDTH)

HSYNC_WIDTH—Hsync width in DI_CLK

with 0.5 DI_CLK resolution. Defined by DI’s

counter.

ns

IP9

Horizontal blank interval 1

Thbi1

BGXP

× Tdicp

BGXP—width of a horizontal blanking

before a first active data in a line (in

interface clocks). The BGXP should be built

by suitable DI’s counter.

ns

IP10

Horizontal blank interval 2

Thbi2

(SCREEN_WIDTH –

BGXP – FW)

× Tdicp

Width a horizontal blanking after a last

active data in a line (in interface clocks)

FW—with of active line in interface clocks.

The FW should be built by suitable DI’s

counter.

ns

IP12

Screen height

Tsh

(SCREEN_HEIGHT)

× Tsw

SCREEN_HEIGHT— screen height in lines

with blanking.

The SCREEN_HEIGHT is a distance

between 2 VSYNCs.

The SCREEN_HEIGHT should be built by

suitable DI’s counter.

ns

IP13

VSYNC width

Tvsw

VSYNC_WIDTH

VSYNC_WIDTH—Vsync width in DI_CLK

with 0.5 DI_CLK resolution. Defined by DI’s

counter

ns

IP14

Vertical blank interval 1

Tvbi1

BGYP

× Tsw

BGYP—width of first Vertical

blanking interval in line.The BGYP should

be built by suitable DI’s counter.

ns

IP15

Vertical blank interval 2

Tvbi2

(SCREEN_HEIGHT –

BGYP – FH)

× Tsw

Width of second Vertical

blanking interval in line.The FH should be

built by suitable DI’s counter.

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MCM16Y1BACFT16 | 16-BIT, MROM, MICROCONTROLLER, PQFP160 |

| MCM16Y1BGCFT16 | 16-BIT, MROM, MICROCONTROLLER, PQFP160 |

| M68HC16Y1CFC | 16-BIT, MROM, MICROCONTROLLER, PQFP16 |

| MCV14AI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

| MCV14ATI/SL | 8-BIT, FLASH, 20 MHz, RISC MICROCONTROLLER, PDSO14 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MCIMX537CVV8C | 制造商:Freescale Semiconductor 功能描述:IC 32-BIT MPU 800 MHZ 529-BGA |

| MCIMX537CVV8CR2 | 功能描述:處理器 - 專門應(yīng)用 iMX53 Rev 2.1 Indust RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX538DZK1C | 功能描述:處理器 - 專門應(yīng)用 I.MX53 2.1 POP RoHS:否 制造商:Freescale Semiconductor 類型:Multimedia Applications 核心:ARM Cortex A9 處理器系列:i.MX6 數(shù)據(jù)總線寬度:32 bit 最大時鐘頻率:1 GHz 指令/數(shù)據(jù)緩存: 數(shù)據(jù) RAM 大小:128 KB 數(shù)據(jù) ROM 大小: 工作電源電壓: 最大工作溫度:+ 95 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MAPBGA-432 |

| MCIMX53EVK | 制造商:Freescale Semiconductor 功能描述: |

| MCIMX53-LVDS | 制造商:Freescale Semiconductor 功能描述:I.MX53 XGA DISPLAY LVDS DEV BOARD 制造商:Freescale Semiconductor 功能描述:I.MX53, XGA DISPLAY, LVDS, DEV BOARD 制造商:Freescale Semiconductor 功能描述:I.MX53, XGA DISPLAY, LVDS CONNECTOR, DEV BOARD; Silicon Manufacturer:Freescale; Core Architecture:ARM; Core Sub-Architecture:Cortex-A8; Silicon Core Number:i.MX5; Silicon Family Name:i.MX53 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。