- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370782 > HYB18T256324F-22 (INFINEON TECHNOLOGIES AG) 256-Mbit GDDR3 DRAM [600MHz] PDF資料下載

參數(shù)資料

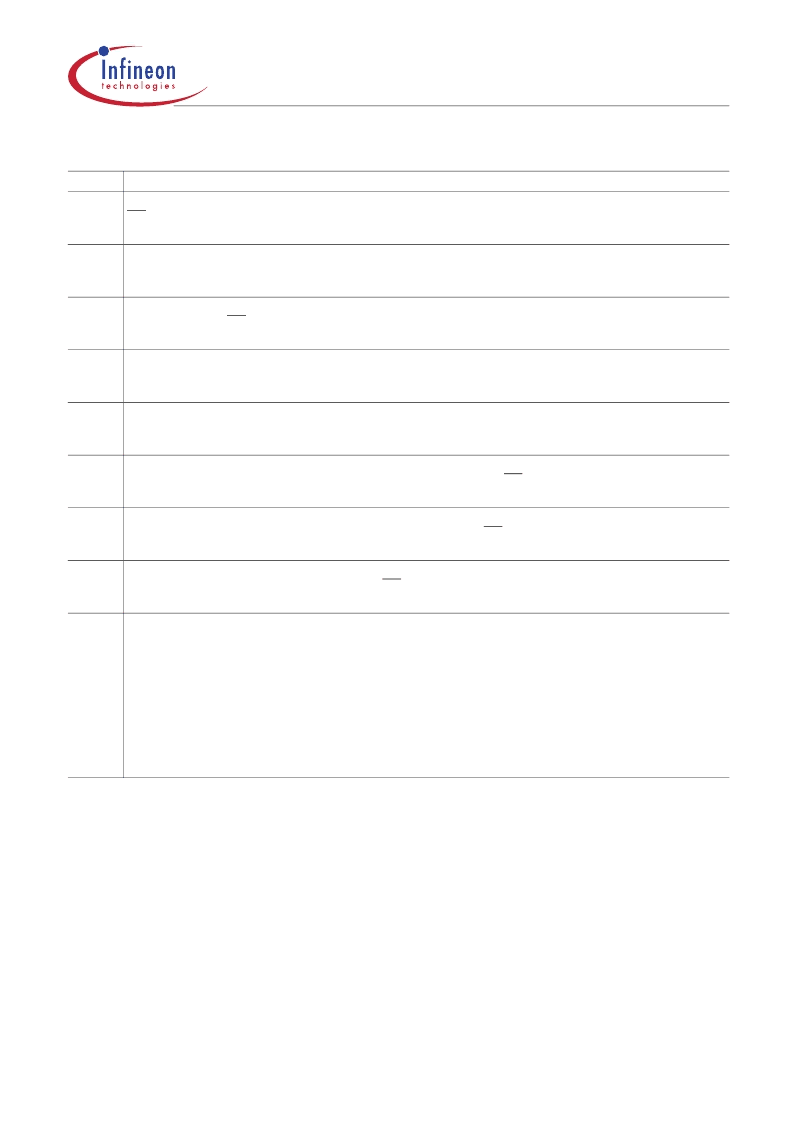

| 型號(hào): | HYB18T256324F-22 |

| 廠商: | INFINEON TECHNOLOGIES AG |

| 英文描述: | 256-Mbit GDDR3 DRAM [600MHz] |

| 中文描述: | 256兆GDDR3顯示內(nèi)存[600MHz的] |

| 文件頁(yè)數(shù): | 74/80頁(yè) |

| 文件大小: | 2026K |

| 代理商: | HYB18T256324F-22 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)當(dāng)前第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)

HYB18T256324F–[16/20/22]

256-Mbit DDR SGRAM

Electrical Characteristics

Data Sheet

74

Rev. 1.11, 04-2005

10292004-DOXT-FS0U

1. Data Bus consists of DQ, DM, WDQS

2. Definitions for IDD : LOW is defined as VIN = 0.4 x

V

DDQ

; HIGH is defined as

V

IN

=

V

DDQ

;

STABLE is defined as inputs are stable at a HIGH level.

SWITCHING is defined as inputs are changing between HIGH and LOW every clock cycle for address and

control signals, and inputs changing 50% of each data transfer for DQ signals.

3. Legend : A=Activate, RA=Read with Autoprecharge, D=DESELECT

I

DD2Q

Precharge Quiet Standby Current

CS is HIGH, all banks idle, CKE is HIGH,

t

CK

=min(

t

CK

), Address and other control inputs STABLE, Data

bus inputs are STABLE.

Active Power-Down Standby Current

All banks active, CKE is LOW, Address and control inputs are STABLE; Data bus inputs are STABLE;

standard active power-down mode.

Active Standby Current

All banks active, CS is HIGH, CKE is HIGH,

t

RC

=max(

t

RAS

),

t

CK

=min(

t

CK

); Address and control inputs

are SWITCHING; Data bus inputs are SWITCHING;

I

out

= 0 mA.

Operating Current - Burst Read

All banks active; Continuous read bursts, CL = CL(min);

t

CK=min(

t

CK

); Address and control inputs are

SWITCHING; Data bus inputs are SWITCHING.

Operating Current - Burst Write

All banks active; Continuous write bursts;

t

CK

=min(

t

CK

); Address and control inputs are SWITCHING;

Data bus inputs are SWITCHING.

Burst Auto Refresh Current

Refresh command at

t

RC

=min(

t

RFC

);

t

CK

=min(

t

CK

); CKE is HIGH, CS is HIGH between all valid

commands; Other command and address inputs are SWITCHING; Data bus inputs are SWITCHING.

Distributed Auto Refresh Current

tCK=tCKmin; Refresh command every tREFI; CKE is HIGH, CS is HIGH between valid commands;

Other command and address inputs are SWITCHING; Data bus inputs are SWITCHING.

Self Refresh Current

CKE

≤

max(

V

IL

), external clock off, CK and CK LOW; Address and control inputs are STABLE; Data

Bus inputs are STABLE.

Operating Bank Interleave Read Current

1. All banks interleaving with CL = CL(min); tRCD = tRCDRD(min); tRRD = tRRD(min); Iout=0mA;

Address and control inputs are STABLE during DESELECT; Data bus inputs are SWITCHING.

2: Timing pattern:

-1.6 (600 MHz, CL=7) :

t

CK

= 2.5ns,

t

RCDRD

= 7.

t

CK

;

t

RRD

= 4.

t

CK

;

t

RC

= 18.

t

CK

Read: A0 RA3 D D A1 D D RA0 A2 D D RA1 A3 D D RA2 D D TBD TBD TBD

-2.0 (500 MHz, CL7) :

t

CK

= 2.0ns,

t

RCDRD

= 7.

t

CK

;

t

RRD

= 4.

t

CK

;

t

RC

= 18.

t

CK

Read: A0 RA3 D D A1 D D RA0 A2 D D RA1 A3 D D RA2 D D

-2.2 (455 MHz, CL6) :

t

CK

= 2.2ns,

t

RCDRD

= 7.

t

CK

;

t

RRD

= 4.

t

CK

;

t

RC

= 18.

t

CK

Read: A0 RA3 D D A1 D D RA0 A2 D D RA1 A3 D D RA2 D D

I

DD3P

I

DD3N

I

DD4R

I

DD4W

I

DD5B

I

DD5D

I

DD6

I

DD7

Table 42

Symbol Parameter/Condition

Operating Current Measurement Conditions

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HYB18T256400AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256160A-3S | 256 Mbi t DDR2 SDRAM |

| HYB18T256800AFL-3 | 256 Mbi t DDR2 SDRAM |

| HYB18T256400AFL-37 | 256 Mbi t DDR2 SDRAM |

| HYB18T256800AFL-37 | 256 Mbi t DDR2 SDRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HYB18T256400AF-3.7 | 制造商:Infineon Technologies AG 功能描述:64M X 4 DDR DRAM, 0.5 ns, PBGA60 |

| HYB18T256400AF-5 | 制造商:Infineon Technologies AG 功能描述:SDRAM, DDR, 64M x 4, 60 Pin, Plastic, BGA |

| HYB18T256800AF-5 | 制造商:Infineon Technologies AG 功能描述: |

| HYB18T512161BF-25 | 制造商:Qimonda 功能描述:SDRAM, DDR, 32M x 16, 84 Pin, Plastic, BGA |

| HYB18T512400AF-5 | 制造商:Intersil Corporation 功能描述:SDRAM, DDR, 128M x 4, 60 Pin, Plastic, BGA |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。