- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296194 > HMT351V7BFR8C-H9 (HYNIX SEMICONDUCTOR INC) DDR DRAM MODULE, DMA240 PDF資料下載

參數(shù)資料

| 型號: | HMT351V7BFR8C-H9 |

| 廠商: | HYNIX SEMICONDUCTOR INC |

| 元件分類: | DRAM |

| 英文描述: | DDR DRAM MODULE, DMA240 |

| 封裝: | ROHS COMPLIANT, DIMM-240 |

| 文件頁數(shù): | 49/61頁 |

| 文件大小: | 1050K |

| 代理商: | HMT351V7BFR8C-H9 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當(dāng)前第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

Rev. 0.1 / Feb. 2010

53

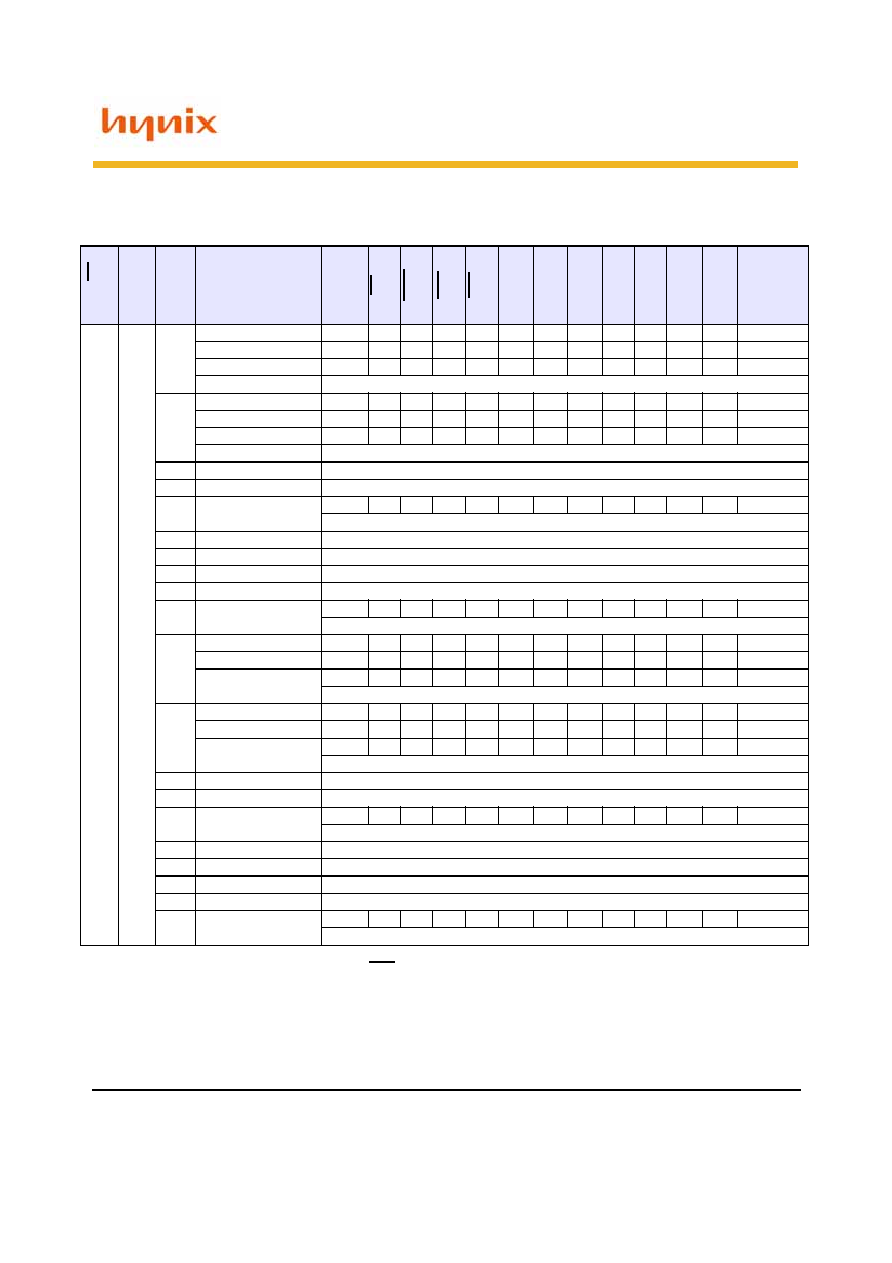

Table 10 - IDD7 Measurement-Loop Patterna)

ATTENTION! Sub-Loops 10-19 have inverse A[6:3] Pattern and Data Pattern than Sub-Loops 0-9

a) DM must be driven LOW all the time. DQS, DQS are used according to RD Commands, otherwise MID-LEVEL.

b) Burst Sequence driven on each DQ signal by Read Command. Outside burst operation, DQ signals are MID-LEVEL.

CK,

CK

CKE

Sub-Loop

Cyc

le

Number

C

o

mmand

CS

RAS

CAS

WE

OD

T

BA[

2

:0]

A[1

5

:1

1]

A[1

0

]

A[9:7]

A[6:3]

A[2

:0]

Datab)

to

ggl

ing

St

atic

Hig

h

00

ACT

0

1

0

00

0

-

1

RDA

0

1

0

1

0

00

1

0

00000000

2D

1

0

00

0

-

...

repeat above D Command until nRRD - 1

1

nRRD

ACT

0

1

0

1

00

0

F

0

-

nRRD+1

RDA

0

1

0

1

0

1

00

1

0

F

0

00110011

nRRD+2

D

1

0

1

00

0

F

0

-

...

repeat above D Command until 2* nRRD - 1

2

2*nRRD

repeat Sub-Loop 0, but BA[2:0] = 2

3

3*nRRD

repeat Sub-Loop 1, but BA[2:0] = 3

4

4*nRRD

D1

0

3

00

0

F

0

-

Assert and repeat above D Command until nFAW - 1, if necessary

5

nFAW

repeat Sub-Loop 0, but BA[2:0] = 4

6

nFAW+nRRD

repeat Sub-Loop 1, but BA[2:0] = 5

7

nFAW+2*nRRD

repeat Sub-Loop 0, but BA[2:0] = 6

8

nFAW+3*nRRD

repeat Sub-Loop 1, but BA[2:0] = 7

9

nFAW+4*nRRD

D1

0

7

00

0

F

0

-

Assert and repeat above D Command until 2* nFAW - 1, if necessary

10

2*nFAW+0

ACT

0

1

0

00

0

F

0

-

2*nFAW+1

RDA

0

1

0

1

0

00

1

0

F

0

00110011

2&nFAW+2

D1

0

00

0

F

0

-

Repeat above D Command until 2* nFAW + nRRD - 1

11

2*nFAW+nRRD

ACT

0

1

0

1

00

0

-

2*nFAW+nRRD+1

RDA

0

1

0

1

0

1

00

1

0

00000000

2&nFAW+nRRD+2

D1

0

1

00

0

-

Repeat above D Command until 2* nFAW + 2* nRRD - 1

12

2*nFAW+2*nRRD

repeat Sub-Loop 10, but BA[2:0] = 2

13

2*nFAW+3*nRRD

repeat Sub-Loop 11, but BA[2:0] = 3

14

2*nFAW+4*nRRD

D1

0

3

00

0

-

Assert and repeat above D Command until 3* nFAW - 1, if necessary

15

3*nFAW

repeat Sub-Loop 10, but BA[2:0] = 4

16

3*nFAW+nRRD

repeat Sub-Loop 11, but BA[2:0] = 5

17

3*nFAW+2*nRRD

repeat Sub-Loop 10, but BA[2:0] = 6

18

3*nFAW+3*nRRD

repeat Sub-Loop 11, but BA[2:0] = 7

19

3*nFAW+4*nRRD

D1

0

7

00

0

-

Assert and repeat above D Command until 4* nFAW - 1, if necessary

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HN4400 | NPN EXPITAXIAL SILICON TRANSISTOR |

| HN5400 | PNP Silicon Expitaxial Planar Transistor for general purpose, high voltage amplifier applications |

| HN5401 | PNP Silicon Expitaxial Planar Transistor for general purpose, high voltage amplifier applications |

| HN546 | NPN Silicon Epitaxial Planar Transistor |

| HN547 | NPN Silicon Epitaxial Planar Transistor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMT351V7BMR4C-G7 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR4C-H9 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR8C-G7 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7BMR8C-H9 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:240pin DDR3 SDRAM VLP Registered DIMM |

| HMT351V7CFR4A | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:DDR3L SDRAM VLP Registered DIMM Based on 2Gb C-die |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。