- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370212 > FMMT560A PDF資料下載

參數(shù)資料

| 型號: | FMMT560A |

| 文件頁數(shù): | 7/247頁 |

| 文件大小: | 2493K |

| 代理商: | FMMT560A |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁第238頁第239頁第240頁第241頁第242頁第243頁第244頁第245頁第246頁第247頁

5

www.fairchildsemi.com

FM24C256 rev. A.2

F

BACKGROUND INFORMATION (I

2

C Bus)

As mentioned, the I

2

C bus allows synchronous bidirectional com-

munication between Transmitter/Receiver using the SCL (clock)

and SDA (Data I/O) lines. All communication must be started with a

valid START condition, concluded with a STOP condition and

acknowledged by the Receiver with an ACKNOWLEDGE condition.

In addition, since the I

2

C bus is designed to support other devices

such as RAM, EPROM, etc., the device type identifier string, or

control byte, must follow the START condition. For EEPROMs, the

first 4-bit of the control byte is 1010 binary for READ and WRITE

operations. This is then followed by the device selection bits A2, A1

and A0, and acts as the three most significant bits of the word

address.The final bit in the control byte determines the type of

operation performed (READ/WRITE). A "1" signifies a READ while

a "0" signifies a WRITE. The control byte is then followed by two bytes

that define the word address, which is then followed by the data byte.

The EEPROMs on the I

2

C bus may be configured in any manner

required, providing the total memory addressed does not exceed

512K bits (64K bytes). EEPROM memory addressing is controlled

by hardware configuring the A2, A1, and A0 pins (Device Address

pins) with pull-up or pull-down resistors. ALL UNUSED PINS

MUST BE GROUNDED (tied to V

SS

).

Addressing an EEPROM memory location involves sending a

command string with the following information:

[DEVICE TYPE]-[DEVICE ADDRESS]-[PAGE BLOCK AD-

DRESS]-[BYTE ADDRESS]

Pin Description

SERIAL CLOCK (SCL)

Definitions

Word

8 bits (byte) of data

Page

64 sequential addresses (one byte each) that

may be programmed during a "Page Write"

programming cycle.

Master

Any I

2

C device CONTROLLING the transfer of

data (such as a microcontroller).

Slave

Device being controlled (EEPROMS are

always considered Slaves).

Transmitter

Device currently SENDING data on the bus

(may be either a Master or Slave).

Receiver

Device currently receiving data on the bus

(Master or Slave).

The SCL input is used to clock all data into and out of the device.

SERIAL DATA (SDA)

SDA is a bidirectional pin used to transfer data to and from the

device. It is an open drain output and may be wire-ORed with any

number of open drain or open collector outputs.

Device Address Inputs (A0, A1, A2)

Device address pins A0, A1, and A2 are connected to V

or V

to configure the EEPROM address for multiple device configura-

tion. A total of eight different devices can be attached to the same

SDA bus.

Write Protection (WP

)

If WP is tied to V

, program WRITE operations onto the entire

array of the memory will not be executed. READ operations are

always available.

If WP is tied to V

, normal memory operation is enabled for

READ/WRITE over the entire 256K bit memory array.

This feature allows the user to assign the entire array of the memory

as ROM, which can be protected against accidental programming

writes. When WRITE is disabled, slave address and word address

will be acknowledged but data will not be acknowledged.

Device Operation

The FM24C256xxx supports a bidirectional bus oriented protocol.

The protocol defines any device that sends data onto the bus as a

transmitter and the receiving devices as the receiver. The device

controlling the transfer is the master and the device that is con-

trolled is the slave. The master will always initiate data transfers and

provide the clock for both transmit and receive operations. There-

fore, the FM24C256xxx is considered a slave in all applications.

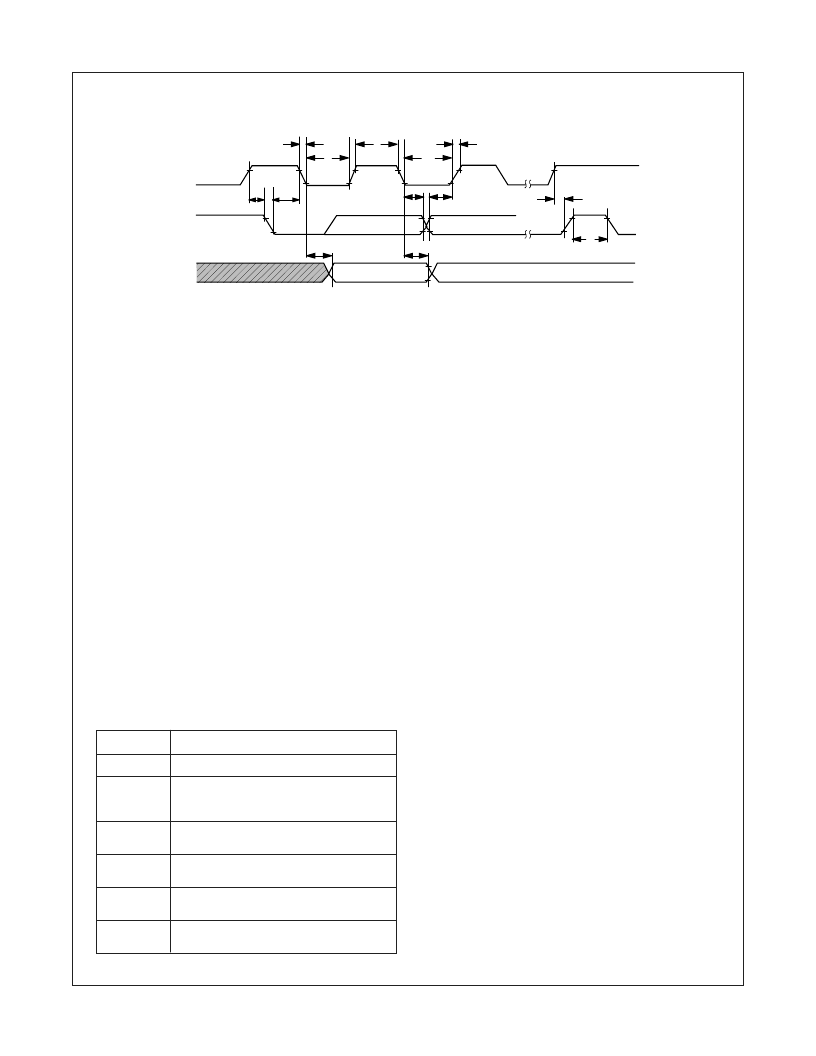

CLOCK AND DATA CONVENTIONS

Data states on the SDA line can change only during SCL LOW.

SDA state changes during SCL HIGH and are reserved for

indication of start and stop conditions. Refer to Figures 1 and 2.

START CONDITION

All commands are preceded by the start condition, which is a

HIGH to LOW transition of SDA when SCL is HIGH. The

FM24C256xxx continuously monitors the SDA and SCL lines for

the start condition and will not respond to any command until this

condition has been met.

STOP CONDITION

All communications are terminated by a stop condition, which is a

LOW to HIGH transition of SDA when SCL is HIGH. The stop

condition is also used by the FM24C256xxx to place the device in

the standby power mode.

SCL

SDA

IN

SDA

OUT

tF

tLOW

tHIGH

tR

tLOW

tAA

tDH

tBUF

tSU:STA

tHD:DAT

tHD:STA

tSU:DAT

tSU:STO

DS800023-3

Bus Timing

Note 3:

SCL = Serial Clock Data

SDA = Serial Data I/O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMMT92CSM | General Purpose PNP Transistor In a Hermetically Sealed Ceramic Surface Mount Package(通用PNP晶體管( 陶瓷表貼封裝)) |

| FMMT92CSM | GENERAL PURPOSE PNP TRANSISTOR IN A HERMETICALLY SEALED CERAMIC SURFACE MOUNT PACKAGE |

| FMN1.1 | TRANSISTOR | MOSFET | N-CHANNEL | 30V V(BR)DSS | CHIP |

| FMN1.2 | TRANSISTOR | MOSFET | N-CHANNEL | 33V V(BR)DSS | CHIP |

| FMN35.3 | TRANSISTOR | MOSFET | N-CHANNEL | 33V V(BR)DSS | CHIP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FMMT560TA | 功能描述:兩極晶體管 - BJT PNP High V 500V RoHS:否 制造商:STMicroelectronics 配置: 晶體管極性:PNP 集電極—基極電壓 VCBO: 集電極—發(fā)射極最大電壓 VCEO:- 40 V 發(fā)射極 - 基極電壓 VEBO:- 6 V 集電極—射極飽和電壓: 最大直流電集電極電流: 增益帶寬產(chǎn)品fT: 直流集電極/Base Gain hfe Min:100 A 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PowerFLAT 2 x 2 |

| FMMT560TC | 功能描述:兩極晶體管 - BJT PNP HighV 500V RoHS:否 制造商:STMicroelectronics 配置: 晶體管極性:PNP 集電極—基極電壓 VCBO: 集電極—發(fā)射極最大電壓 VCEO:- 40 V 發(fā)射極 - 基極電壓 VEBO:- 6 V 集電極—射極飽和電壓: 最大直流電集電極電流: 增益帶寬產(chǎn)品fT: 直流集電極/Base Gain hfe Min:100 A 最大工作溫度: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PowerFLAT 2 x 2 |

| FMMT576 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述: |

| FMMT589 | 制造商:Diodes Incorporated 功能描述:TRANSISTOR PNP SOT-23 |

| FMMT589 | 制造商:Diodes Incorporated 功能描述:TRANSISTOR PNP SOT-23 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。