- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄298813 > AD9874ABSTZ (ANALOG DEVICES INC) SPECIALTY TELECOM CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | AD9874ABSTZ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | 通信及網(wǎng)絡(luò) |

| 英文描述: | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| 封裝: | PLASTIC, MS-026BBC, LQFP-48 |

| 文件頁數(shù): | 34/40頁 |

| 文件大小: | 1682K |

| 代理商: | AD9874ABSTZ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁

REV. A

AD9874

–4–

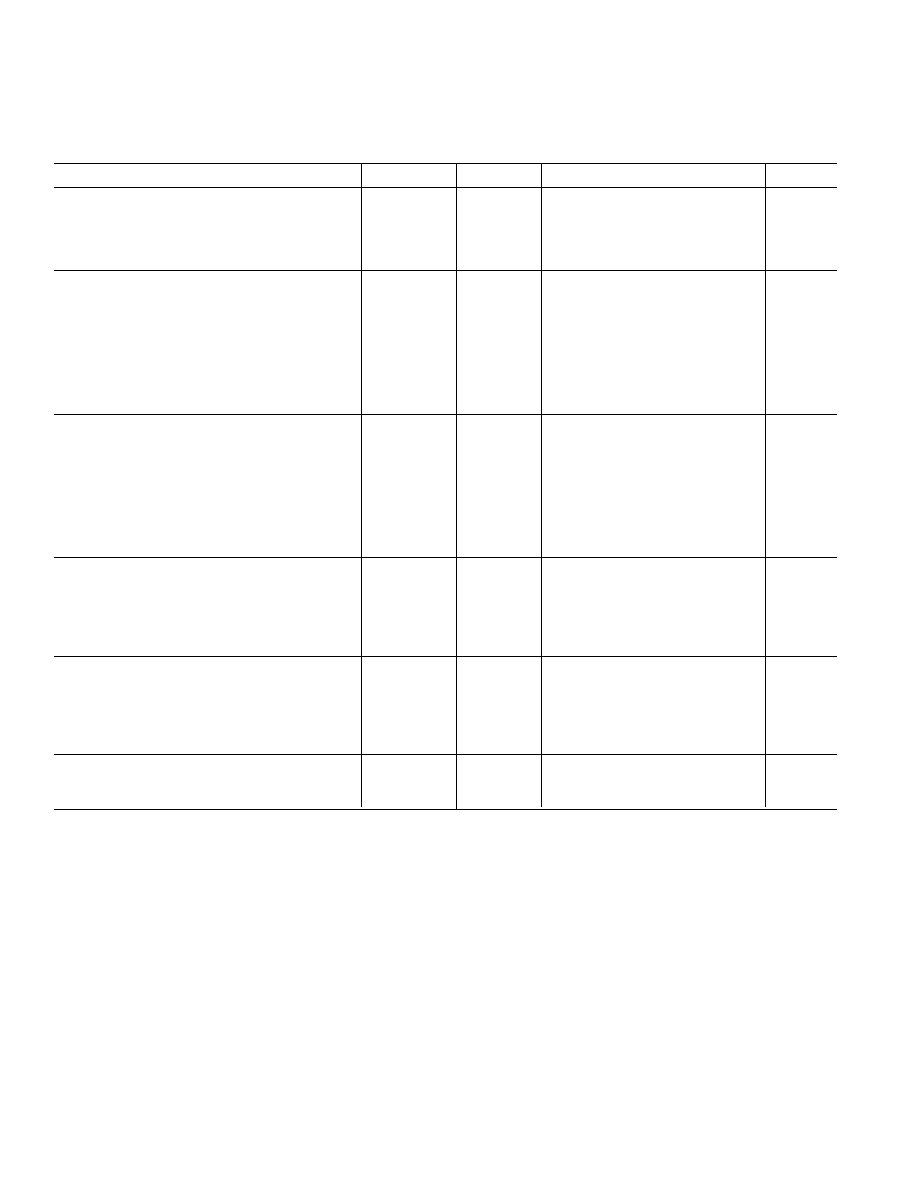

DIGITAL SPECIFICATIONS (VDDI = VDDF = VDDA = VDDC = VDDL = VDDD = VDDH = 2.7 V to 3.6 V, VDDQ = VDDP = 2.7 V to 5.5 V,

fCLK = 18 MSPS, fIF = 109.65 MHz, fLO = 107.4 MHz, fREF = 16.8 MHz, unless otherwise noted.)

1

Parameter

Temp

Test Level

Min

Typ

Max

Unit

DECIMATOR

Decimation Factor

2

Full

IV

48

960

Pass-Band Width

Full

V

50%

fCLKOUT

Pass-Band Gain Variation

Full

IV

1.2

dB

Alias Attenuation

Full

IV

88

dB

SPI-READ OPERATION (See Figure 1a)

PC Clock Frequency

Full

IV

10

MHz

PC Clock Period (tCLK)

Full

IV

100

ns

PC Clock HI (tHI)

Full

IV

45

ns

PC Clock LOW (tLOW)

Full

IV

45

ns

PC to PD Setup Time (tDS)

Full

IV

2

ns

PC to PD Hold Time (tDH)

Full

IV

2

ns

PE to PC Setup Time (t

S)

Full

IV

5

ns

PC to

PE Hold Time (t

H)

Full

IV

5

ns

SPI-WRITE OPERATION

3 (See Figure 1b)

PC Clock Frequency

Full

IV

10

MHz

PC Clock Period (tCLK)

Full

IV

100

ns

PC Clock HI (tHI)

Full

IV

45

ns

PC Clock LOW (tLOW)

Full

IV

45

ns

PC to PD Setup Time (tDS)

Full

IV

2

ns

PC to PD Hold Time (tDH)

Full

IV

2

ns

PC to PD (or DOUBT) Data Valid Time (tDV)

Full

IV

3

ns

PE to PD Output Valid to Hi-Z (t

EZ)

Full

IV

8

ns

SSI

3 (see Figure 2b)

CLKOUT Frequency

Full

IV

0.867

26

MHz

CLKOUT Period (tCLK)

Full

IV

38.4

1153

ns

CLKOUT Duty Cycle (tHI, tLOW)

Full

IV

33

50

67

ns

CLKOUT to FS Valid Time (tV)

Full

IV

–1

+1

ns

CLKOUT to DOUT Data Valid Time (tDV)

Full

IV

–1

+1

ns

CMOS LOGIC INPUTS

4

Logic “1” Voltage (VIH)

Full

IV

VDDH – 0.2

V

Logic “0” Voltage (VIL)

Full

IV

0.5

V

Logic “1” Current (VIH)

Full

IV

10

A

Logic “0” Current (VIL)

Full

IV

10

A

Input Capacitance

Full

IV

3

pF

CMOS LOGIC OUTPUTS

3, 4, 5

Logic “1” Voltage (VIH)

Full

IV

VDDH – 0.2

V

Logic “0” Voltage (VIL)

Full

IV

0.2

V

NOTES

1Standard operating mode: high IIP3 setting, synthesizers in normal (not fast acquire) mode, f

CLK = 18 MHz, decimation factor = 300, 10 pF load on SSI output pins:

VDDx = 3.0 V.

2Programmable in steps of 48 or 60.

3CMOS output mode with C

LOAD = 10 pF and Drive Strength = 7.

4Absolute Max and Min input/output levels are VDDH +0.3 V and –0.3 V.

5I

OL = 1 mA; specification is also dependent on Drive Strength setting.

Specifications subject to change without notice.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD9874ABSTZRL | SPECIALTY TELECOM CIRCUIT, PQFP48 |

| ADC0831CIWM | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO14 |

| ADE7116ASTZF8-RL | SPECIALTY ANALOG CIRCUIT, PQFP64 |

| ADE7753ARSZRL | SPECIALTY ANALOG CIRCUIT, PDSO20 |

| ADEX-R10+ | 10 MHz - 1000 MHz RF/MICROWAVE DOUBLE BALANCED MIXER, 8.3 dB CONVERSION LOSS-MAX |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD9874BST | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| AD9874EB | 制造商:AD 制造商全稱:Analog Devices 功能描述:IF Digitizing Subsystem |

| AD9874-EB | 制造商:Analog Devices 功能描述: |

| AD9874-EBZ | 功能描述:BOARD EVAL FOR AD9874 制造商:analog devices inc. 系列:- 零件狀態(tài):有效 類型:數(shù)字轉(zhuǎn)換器 頻率:10MHz ~ 300MHz 配套使用產(chǎn)品/相關(guān)產(chǎn)品:AD9874 所含物品:板 標(biāo)準(zhǔn)包裝:1 |

| AD9875 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Broadband Modem Mixed-Signal Front End |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。