- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄366235 > 62371AB (Intel Corp.) multi-function PCI device(多功能PCI設(shè)備) PDF資料下載

參數(shù)資料

| 型號(hào): | 62371AB |

| 廠商: | Intel Corp. |

| 英文描述: | multi-function PCI device(多功能PCI設(shè)備) |

| 中文描述: | 多功能PCI設(shè)備(多功能的PCI設(shè)備) |

| 文件頁(yè)數(shù): | 143/284頁(yè) |

| 文件大小: | 1042K |

| 代理商: | 62371AB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)當(dāng)前第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)第234頁(yè)第235頁(yè)第236頁(yè)第237頁(yè)第238頁(yè)第239頁(yè)第240頁(yè)第241頁(yè)第242頁(yè)第243頁(yè)第244頁(yè)第245頁(yè)第246頁(yè)第247頁(yè)第248頁(yè)第249頁(yè)第250頁(yè)第251頁(yè)第252頁(yè)第253頁(yè)第254頁(yè)第255頁(yè)第256頁(yè)第257頁(yè)第258頁(yè)第259頁(yè)第260頁(yè)第261頁(yè)第262頁(yè)第263頁(yè)第264頁(yè)第265頁(yè)第266頁(yè)第267頁(yè)第268頁(yè)第269頁(yè)第270頁(yè)第271頁(yè)第272頁(yè)第273頁(yè)第274頁(yè)第275頁(yè)第276頁(yè)第277頁(yè)第278頁(yè)第279頁(yè)第280頁(yè)第281頁(yè)第282頁(yè)第283頁(yè)第284頁(yè)

E

7.2.10.

82371AB (PIIX4)

143

4/9/97 2:23 PM PIIX4aDS

INTEL CONFIDENTIAL

(until publication date)

PRELIMINARY

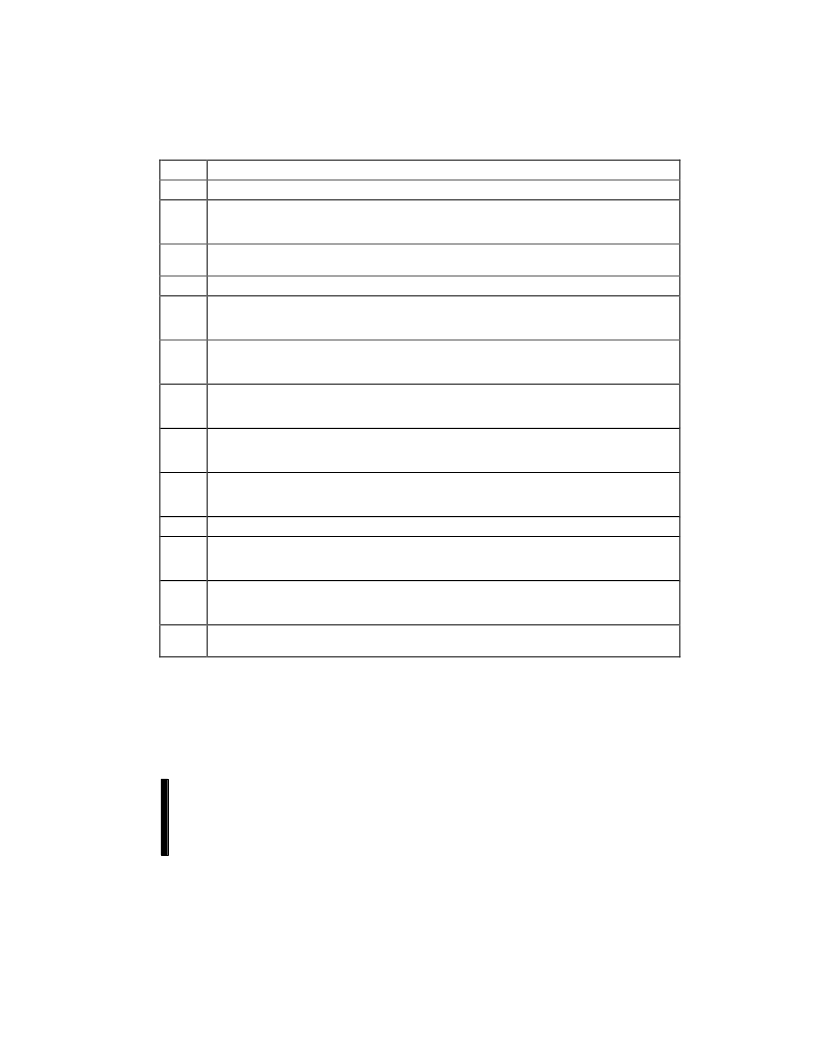

GLBSTS—GLOBAL STATUS REGISTER (IO)

I/O Address:

Default Value:

Attribute:

Base + (18h)

00h

Read/Write

Bit

Description

15:12

Reserved.

11

IRQ Resume Status (IRQ_RSM_STS)—R/W.

1=System was resumed from a Powered On

Suspend (POS) state due to an interrupt assertion (IRQ[1,3:15]). 0=System was not resumed due to

IRQ. This bit is only set by hardware and can only be reset by writing a 1 to this bit position.

10

External SMI Status (EXTSMI_STS)—R/WC.

1=EXTSMI# signal was asserted. 0=EXTSMI# was

not asserted. This bit is only set by hardware and can only be reset by writing a 1 to this bit position.

9

Reserved.

8

Global Standby Status (GSTBY_STS)—R/WC.

1=Global Standby timer expired (counted down to

0). 0=Global Standby timer did not expire. This bit is only set by hardware and can only be reset by

writing a 1 to this bit position.

7

GP Status (GP_STS)—RO.

1=Indicates that one of the status bits in the GPSTS register is set.

0=All bits in GPSTS register are reset. This bit can only be reset by resetting all bits in the GPSTS

register.

6

PM1 Status (PM1_STS)—RO.

1=Indicates that one of the status bits in the PMSTS register is set.

0=All bits in PMSTS register are reset. This bit can only be reset by resetting all bits in the PMSTS

register.

5

APM Status (APM_STS)—R/WC.

1=A write occurred to the APMC register causing generation of

an SMI#. 0=A write has not occurred to the APMC register causing generation of an SMI#. This bit is

cleared by writing a 1 to this bit position.

4

All Devices Status (DEV_STS)—RO.

1=Indicates that one of the status bits in the DEV_STS

register is set. 0=All bits in DEV_STS register are reset. This bit can only be reset by resetting all

bits in the DEV_STS register.

3

Reserved.

2

P4MA Status (P4MA_STS)—R/WC.

1=An SMI# was generated due to a PIIX4 PCI cycle being

Master Aborted. 0=No SMI# was generated due to PIIX4 PCI cycles having been Master Aborted.

This bit is only set by hardware and can only be reset by writing a 1 to this bit position.

1

Legacy USB Status (LEGACY_USB_STS)—R/WC.

1=USB legacy keyboard logic

generated an

SMI#. 0=USB legacy keyboard logic did not generate an SMI#. This bit is only set by hardware and

can only be reset clearing the children status bits in the USB status register.

0

BIOS Status (BIOS_STS)—R/WC.

1=A write of 1 occurred to the GBL_RLS bit. 0=A write of 1 did

not occur to the GBL_RLS bit. This bit is set by hardware and is cleared by writing a 1 to it.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 6259 | CONNECTOR ACCESSORY |

| 6273 | 8-BIT LATCHED DMOS POWER DRIVER |

| 6275 | 8-BIT SERIAL-INPUT, CONSTANTCURRENT LATCHED LED DRIVER |

| 6276 | 16-BIT SERIAL-INPUT, CONSTANTCURRENT LATCHED LED DRIVER |

| 6277 | 8-BIT SERIAL-INPUT, CONSTANTCURRENT LATCHED LED DRIVER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 6237201015 | 制造商:Varta 功能描述:2/3 A Series Lithium 3 V 1350 mAh With Sleeve and Wire Cylindrical Battery |

| 6237201301 | 制造商:Varta 功能描述:BATTERY LITHIUM 2/3AA PCB 3V 制造商:Varta 功能描述:BATTERY, LITHIUM, 2/3AA, PCB, 3V 制造商:Varta 功能描述:2/3 AA Lithium 3 V 1350 mAh PCB Cylindrical Battery |

| 62372091322 | 制造商:3M Electronic Products Division 功能描述:HOT MELT ADHESIVELM Q 5/8"X8" 制造商:3M Electronic Products Division 功能描述:SCOTCH-WELD HOT MELT/LOW MELT 5KG 3762M |

| 62372093302 | 制造商:3M Electronic Products Division 功能描述:HOT MELT ADHESIVE |

| 62372098301 | 制造商:3M Electronic Products Division 功能描述:HOT MELT ADHESIVE |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。