- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371435 > 28F1602C3 (Intel Corp.) 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲器和靜態(tài)存儲器) PDF資料下載

參數(shù)資料

| 型號: | 28F1602C3 |

| 廠商: | Intel Corp. |

| 英文描述: | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲器和靜態(tài)存儲器) |

| 中文描述: | 3伏高級堆疊芯片級封裝存儲器(3V的閃速存儲器和靜態(tài)存儲器) |

| 文件頁數(shù): | 18/62頁 |

| 文件大?。?/td> | 538K |

| 代理商: | 28F1602C3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

28F1602C3, 28F3204C3

E

18

PRODUCT PREVIEW

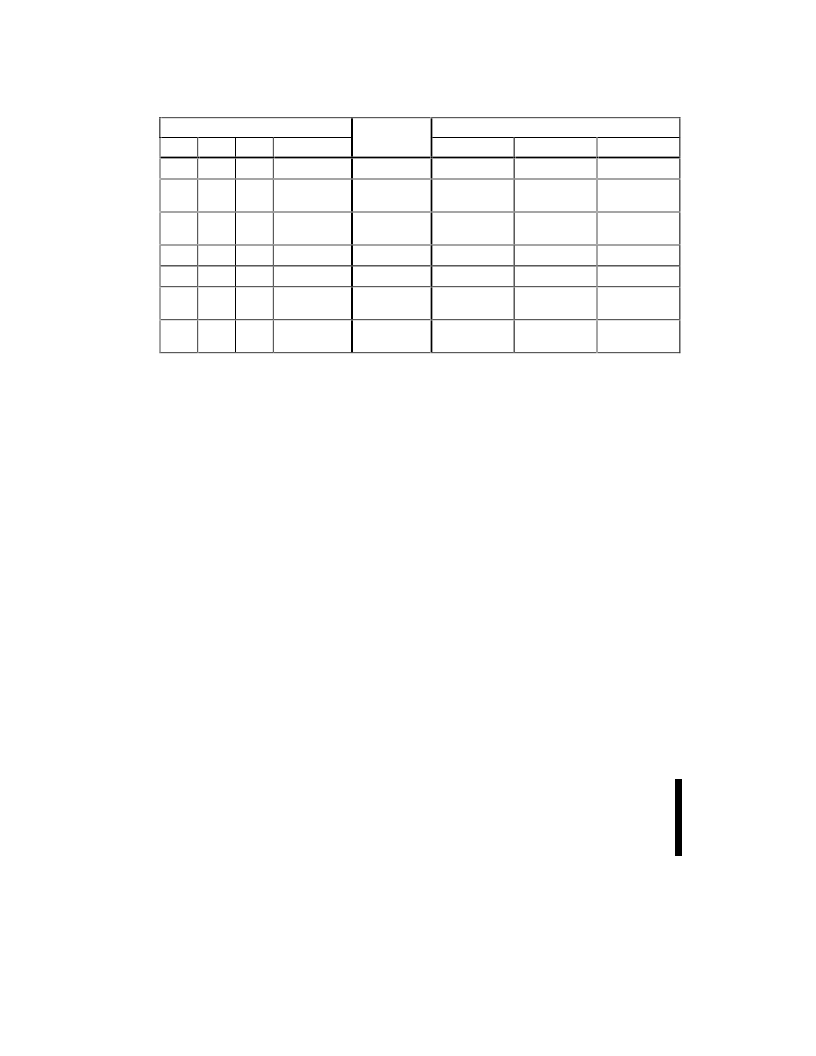

Table 8. Block Locking State Transitions

Current State

Erase/Prog

Lock Command Input Result [Next State]

WP#

DQ

1

DQ

0

Name

Allowed

Lock

Unlock

Lock-Down

0

0

0

“Unlocked”

Yes

Goes To [001]

No Change

Goes To [011]

0

0

1

“Locked”

(Default)

No

No Change

Goes To [000]

Goes To [011]

0

1

1

“Locked-

Down”

No

No Change

No Change

No Change

1

0

0

“Unlocked”

Yes

Goes To [101]

No Change

Goes To [111]

1

0

1

“Locked”

No

No Change

Goes To [100]

Goes To [111]

1

1

0

Lock-Down

Disabled

Yes

Goes To [111]

No Change

Goes To [111]

1

1

1

Lock-Down

Disabled

No

No Change

Goes To [110]

No Change

NOTES:

1.

In this table, the notation [XYZ] denotes the locking state of a block, where X = WP#, Y = DQ

, and Z = DQ

. The current

locking state of a block is defined by the state of WP# and the two bits of the block lock status (DQ

0

, DQ

1

). DQ

0

indicates if

a block is locked (1) or unlocked (0). DQ

1

indicates if a block has been locked-down (1) or not (0).

At power-up or device reset, all blocks default to Locked state [001] (if WP# = 0). Holding WP# = 0 is the recommended

default.

The

“Erase/Program Allowed” column shows whether erase and program operations are enabled (Yes) or disabled (No)

in that block’s current locking state.

The “Lock Command Input Result [Next State]” column shows the result of writing the three locking commands (Lock,

Unlock, Lock-Down) in the current locking state. For example, “Goes To [001]” would mean that writing the command to a

block in the current locking state would change it to [001].

2.

3.

4.

7.1

Reading the Protection

Register

The protection register is read in the configuration

read mode. The device is switched to this mode by

writing the Read Configuration command (90H).

Once in this mode, read cycles from addresses

shown in Appendix E retrieve the specified

information. To return to read array mode, write the

Read Array command (FFH).

7.2

Programming the Protection

Register

The protection register bits are programmed using

the two-cycle Protection Program command. The

64-bit number is programmed 16 bits at a time for

word-wide parts. First write the Protection Program

Setup command, C0H. The next write to the device

will latch in address and data and program the

specified location. The allowable addresses are

shown in Appendix E. See Figure 20 for the

Protection Register Programming Flowchart

Any attempt to address Protection Program

commands outside the defined protection register

address space will result in a status register error

(program error bit SR.4 will be set to 1). Attempting

to program or to a previously locked protection

register segment will result in a status register error

(program error bit SR.4 and lock error bit SR.1 will

be set to 1).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28F3204C3 | 3 V Advanced+ Stacked Chip Scale Package Memory(3V高級堆芯片封裝存儲器) |

| 28F1604C3 | 3 Volt Advanced+ Stacked Chip Scale Package Memory(3V閃速存儲器和靜態(tài)存儲器) |

| 28F160C18 | 1.8V Advanced+ Boot Block Flash Memory(1.8V高級引導(dǎo)塊閃速存儲器) |

| 28F160C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級引導(dǎo)塊閃速存儲器) |

| 28F800C2 | 2.4V Advanced+ Boot Block Flash Memory(2.4V高級引導(dǎo)塊閃速存儲器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28F160B3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| 28F160BJHE-BTLTH | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 28F160C3 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:3 Volt Intel Advanced+ Boot Block Flash Memory |

| 28F160C3BA90 | 制造商: 功能描述: 制造商:Intel 功能描述: 制造商:undefined 功能描述: |

| 28F160C3TD70 | 制造商: 功能描述: 制造商:undefined 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。