- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370034 > 28222-13 (Conexant Systems, Inc.) ATM Transmitter/Receiver with UTOPIA Interface PDF資料下載

參數(shù)資料

| 型號(hào): | 28222-13 |

| 廠商: | Conexant Systems, Inc. |

| 英文描述: | ATM Transmitter/Receiver with UTOPIA Interface |

| 中文描述: | 自動(dòng)柜員機(jī)發(fā)射機(jī)/接收機(jī)的UTOPIA接口 |

| 文件頁數(shù): | 93/161頁 |

| 文件大?。?/td> | 1832K |

| 代理商: | 28222-13 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁當(dāng)前第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁

CN8223

3.0 Registers

ATM Transmitter/Receiver with UTOPIA Interface

3.3 Configuration Control Registers

100046C

Conexant

3-7

1

0

1

0

1

1

1

1

0x01

—

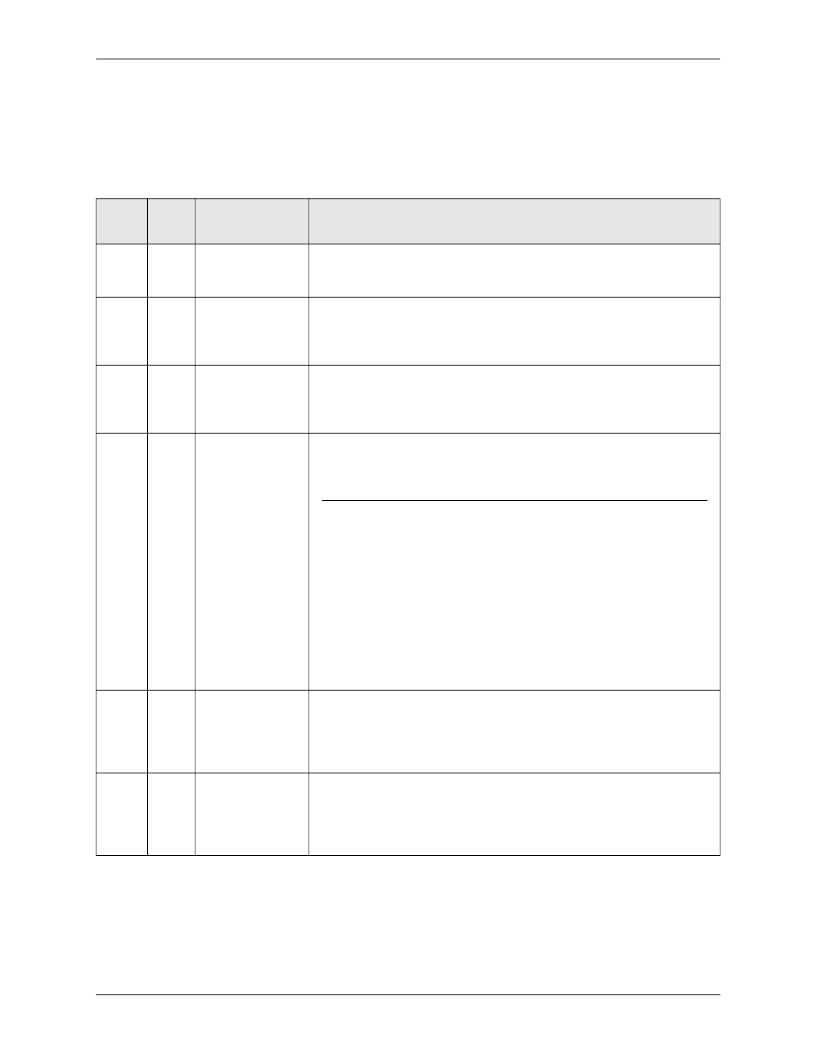

CONFIG_2 (Configuration Control Register 2)

The CONFIG_2 register is located at address 0x01 and controls transmit formatting and alarm generation.

Table 3-4

defines Alarm Controls for the Line Framing/PHY Formats.

Table 3-5

defines the control bits for

STS-1/STS-3c/STM-1.

Table 3-6

defines the overhead bits for Line Framing/PHY Formats.

Bit

Field

Size

Name

Description

15

1

Enable External

Overhead

Enables all overhead octets to be inserted externally in STS-1/STS-3c/STM-1 and

G.832 E3/E4 modes. If this bit is not set, internal generation of overhead octets is

enabled as described in

Section 2.3

.

14

1

All-Zeros FEBE

Inserts an all-0s value in the FEBE field. The all-0s value provides an indication at

the far end that no BIP-8 errors are being detected. BIP-8 status and error counts

are not affected. This control bit is active in all modes whether the FEBE field is

single- or multi-bit.

13

1

All-1s FEBE

Inserts an all-1s value in the FEBE field of the transmit frame. The all-1s value

notifies the far end that the FEBE function is inhibited. BIP-8 status and error counts

are not affected. This control bit is active in all modes whether the FEBE field is

single- or multi-bit.

12

–

10

3

BIP Error Insert

Selects the BIP field that will be errored with the TXFEAC_ERRPAT register

according to the following:

These bits are cleared by the transmitter after the error is inserted in the overhead

field, and can be read as 0 to verify that error insertion has taken place.

9

–

4

6

Transmit Alarm

Control

Controls the generation of alarms for 57-octet PLCPs and internal framers. No

alarms are transmitted if all bits in this control field are set to 0. Setting any of these

bits to a 1 causes an alarm to be transmitted according to

Table 3-4

and

Table 3-5

.

For example, in STS-3c mode, setting bit 4 to a 1 will cause the Line AIS alarm to be

transmitted.

3

–

0

4

Overhead Control

Selectively disables overhead generation. Standard overhead is generated internally

if all bits in this control field are set to 0. Overhead sources for all PHY modes are

given in

Table 2-8

. When a particular overhead field is set to be disabled, it will be

filled with 0s. Overhead generation is disabled dependent on mode, according to the

data in

Table 3-6

.

Bit 12

0

0

0

0

Bit 11

0

0

1

1

Bit 10

0

1

0

1

0

1

0

1

BIP Field to be Errored

No errors inserted

B1 field (all modes)

B2 field, bits 23:16 (STS-3c/STM-1 mode only)

B2 field, bits 15:8 (STS-3c/STM-1 mode only)

B2 field, bits 7:0 (STS-1/STS-3c/STM-1 modes)

B3 field (STS-1/STS-3c/STM-1 modes)

No errors inserted

B2 field, all 3 octets (STS-3c/STM-1 mode)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28222-14 | ATM Transmitter/Receiver with UTOPIA Interface |

| 28233-11 | ATM Transmitter/Receiver with UTOPIA Interface |

| 28C010TRPDB-12 | 150 x 32 pixel format, LED Backlight available |

| 28C010TRT1DE-15 | 1 Megabit (128K x 8-Bit) EEPROM |

| 28C010TRT1DE-20 | 1 Megabit (128K x 8-Bit) EEPROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28222-14 | 制造商:CONEXANT 制造商全稱:CONEXANT 功能描述:ATM Transmitter/Receiver with UTOPIA Interface |

| 282222-003 | 制造商:TE Connectivity 功能描述:81044/12-16-2 - Cable Rools/Shrink Tubing |

| 282223-003 | 制造商:TE Connectivity 功能描述:81044/12-16-3 - Cable Rools/Shrink Tubing |

| 282224-003 | 制造商:TE Connectivity 功能描述:81044/12-16-4 - Cable Rools/Shrink Tubing |

| 282224-1 | 功能描述:汽車連接器 ECONOSEAL RCPT CONT .5MM RoHS:否 制造商:Amphenol SINE Systems 產(chǎn)品:Contacts 系列:ATP 位置數(shù)量: 型式:Female 安裝風(fēng)格: 端接類型: 觸點(diǎn)電鍍:Nickel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。